# **Федеральное государственное автономное образовательное учреждение**высшего образования

# НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ ТОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

На правах рукописи

### Мыцко Евгений Алексеевич

# АЛГОРИТМЫ И АППАРАТНАЯ РЕАЛИЗАЦИЯ НА ПЛИС УСТРОЙСТВ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ПАКЕТНЫХ ИЛИ НЕЗАВИСИМЫХ ОШИБОК ДЛЯ СООБЩЕНИЙ КОРОТКОЙ ДЛИНЫ

05.13.05 – «Элементы и устройства вычислительной техники и систем управления»

# ДИССЕРТАЦИЯ

На соискание ученой степени кандидата технических наук

Научный руководитель д. т. н., доцент Ким Валерий Львович

# ОГЛАВЛЕНИЕ

| ПЕРЕЧЕНЬ | ИСПОЛЬЗУЕМЫХ СОКРАЩЕНИЙ                             | 6    |

|----------|-----------------------------------------------------|------|

| введение | 3                                                   | 7    |

| ГЛАВА 1. | АНАЛИЗ СПОСОБОВ И АЛГОРИТМОВ ОБНАРУЖЕНИЯ            | И    |

| ИСПРАВЛЕ | ЕНИЯ ПАКЕТНЫХ ИЛИ НЕЗАВИСИМЫХ ОШИБОК                | . 21 |

| 1.1. Кл  | ассификация помехоустойчивых кодов                  | . 21 |

| 1.2. Ko  | ды для обнаружения ошибок                           | . 22 |

| 1.2.1.   | Контрольная сумма                                   | . 23 |

| 1.2.2.   | Циклический избыточный код CRC                      | . 24 |

| 1.2.3.   | Параметрическая модель CRC-алгоритма                | . 26 |

| 1.3. Ко  | ды для исправления пакетных или независимых ошибок  | . 28 |

| 1.3.1.   | Систематические помехоустойчивые коды               | . 28 |

| 1.3.2.   | Полиномиальные циклические коды                     | . 32 |

| 1.4. Oc  | новные результаты и выводы по главе                 | . 46 |

| ГЛАВА 2. | АЛГОРИТМЫ, ПРОГРАММЫ И УСТРОЙСТВА                   |      |

| ОБНАРУЖІ | ЕНИЯ ОШИБОК                                         | . 49 |

| 2.1. Ал  | горитмы вычисления CRC                              | . 49 |

| 2.1.1.   | Классический алгоритм                               | . 49 |

| 2.1.2.   | Прямой табличный алгоритм                           | . 50 |

| 2.1.3.   | Обратный табличный алгоритм                         | . 51 |

| 2.1.4.   | Матричный алгоритм                                  | . 53 |

| 2.2. Ис  | следование быстродействия алгоритмов вычисления CRC | . 58 |

| 2.2.1.   | Постановка задачи исследования                      | . 58 |

| 2.2.2.   | Компьютерный эксперимент по вычислению CRC32        | . 59 |

| 2.2.3.   | Анализ результатов компьютерного эксперимента       | . 63 |

| 2.3. Ис  | следование программных реализаций алгоритмов        |      |

| ВЫ       | числения CRC для микропроцессорного устройства      | . 65 |

| 2.3.1.   | Постановка задачи исследования                      | . 65 |

| 2.3.2.   | Описание системы измерения температуры              | . 66 |

| 2.3.3.   | Программная реализация алгоритмов вычисления CRC8      | . 68 |

|----------|--------------------------------------------------------|------|

| 2.3.4.   | Анализ результатов эксперимента                        | . 71 |

| 2.4. Par | зработка устройств вычисления CRC на ПЛИС              | . 73 |

| 2.4.1.   | Постановка задачи                                      | . 73 |

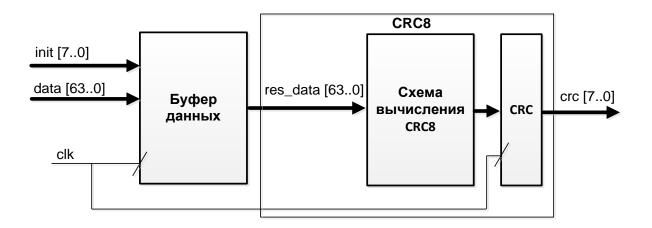

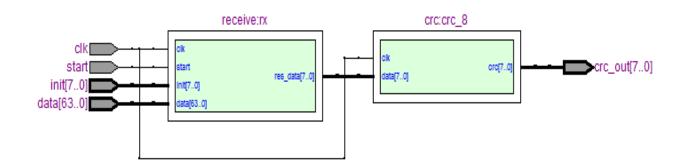

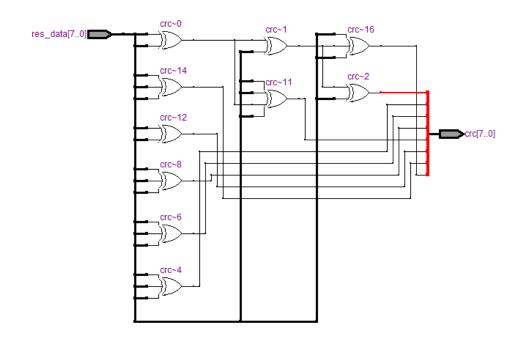

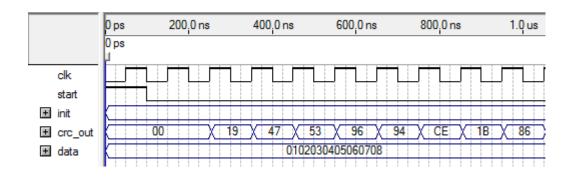

| 2.4.2.   | Разработка устройств вычисления CRC8 на ПЛИС           | . 73 |

| 2.4.3.   | Обсуждение результатов по CRC8                         | . 77 |

| 2.4.4.   | Разработка устройств вычисления CRC32 на ПЛИС          | . 81 |

| 2.4.5.   | Обсуждение результатов по CRC32                        | . 82 |

| 2.5. Per | зультаты и выводы по главе                             | . 86 |

| ГЛАВА 3. | АЛГОРИТМЫ, ПРОГРАММЫ И УСТРОЙСТВА                      |      |

| ИСПРАВЛЕ | ЭИНИЯ ОШИБОК                                           | . 88 |

| 3.1. Ал  | горитм поиска образующих полиномов для кодов,          |      |

| ис       | правляющих независимые ошибки                          | . 88 |

| 3.2. Ко  | мпьютерный эксперимент по поиску образующих            |      |

| ПО       | линомов с применением технологии OpenMP                | . 93 |

|          | Постановка компьютерного эксперимента                  |      |

| 3.2.2.   | Обсуждение результатов                                 | 100  |

| 3.3. Ал  | горитм поиска образующих полиномов для кодов,          |      |

| ис       | правляющих пакетные ошибки                             | 105  |

| 3.4. Ал  | горитмы исправления пакетных и независимых ошибок      | 108  |

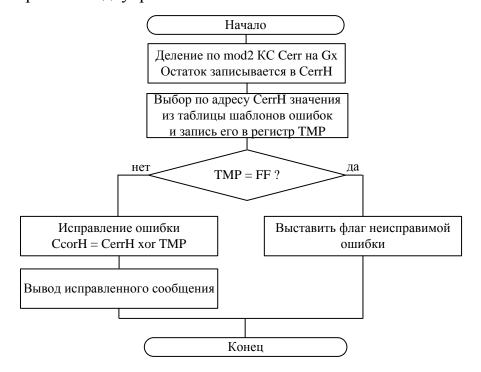

| 3.4.1.   | Табличный алгоритм                                     | 109  |

| 3.4.2.   | Циклический алгоритм для исправления независимых       |      |

|          | ошибок                                                 | 110  |

| 3.4.3.   | Модифицированный циклический алгоритм для              |      |

|          | исправления независимых ошибок                         | 111  |

| 3.4.4.   | Циклический алгоритм для исправления пакетных ошибок   | 113  |

| 3.5. Пр  | ограммная реализация алгоритмов для микропроцессорного |      |

| yc       | гройства                                               | 114  |

| 3.5.1.   | Табличный алгоритм                                     | 115  |

| 3.5.2. Циклический алгоритм                                       |

|-------------------------------------------------------------------|

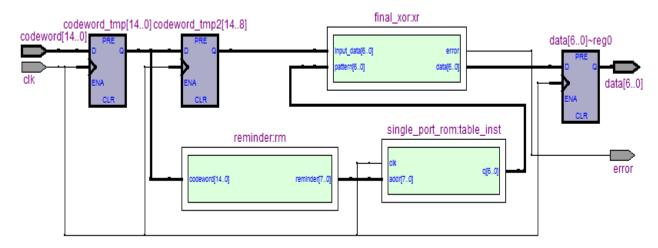

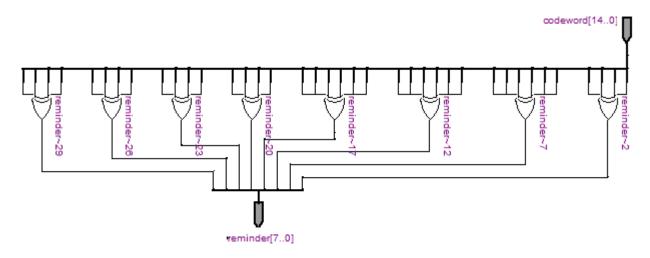

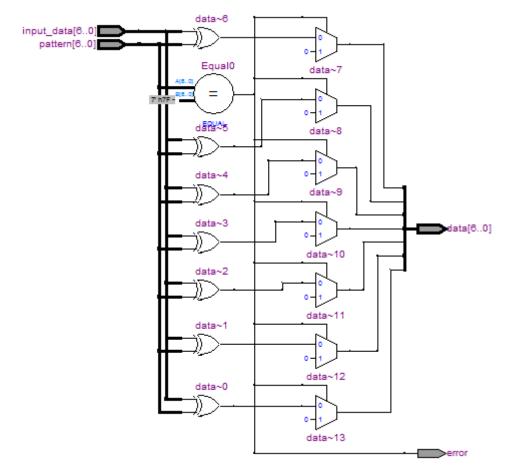

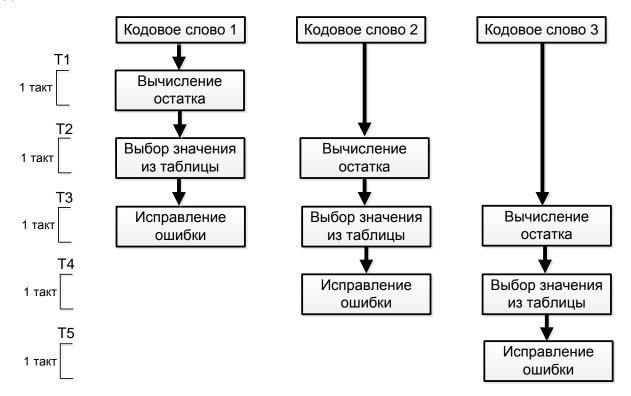

| 3.6. Разработка устройств исправления независимых ошибок на       |

| ПЛИС                                                              |

| 3.6.1. Разработка устройств на ПЛИС для исправления ошибок с      |

| применением кода БЧХ (15,7,5)                                     |

| 3.6.2. Разработка устройств на ПЛИС для исправления ошибок с      |

| применением кода (17, 9, 5)                                       |

| 3.6.3. Разработка устройств на ПЛИС для исправления ошибок с      |

| применением укороченного кода БЧХ (19, 9, 5) 137                  |

| 3.6.4. Обсуждение результатов и сравнение                         |

| 3.7. Разработка устройств исправления пакетных ошибок на ПЛИС 147 |

| 3.7.1. Разработка устройств на ПЛИС для исправления пакетных      |

| ошибок с применением кода (15, 8, 3) 147                          |

| 3.7.2. Разработка устройств на ПЛИС для исправления пакетных      |

| ошибок с применением аналога кода Рида-Соломона (7, 3) 154        |

| 3.8. Основные результаты и выводы по главе                        |

| ГЛАВА 4. ПРАКТИЧЕСКОЕ ПРИМЕНЕНИЕ УСТРОЙСТВ                        |

| ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК НА ПЛИС 162                      |

| 4.1. Разработка устройства исправления ошибок на ПЛИС для         |

| подсистемы синхронизации системы управления                       |

| электрофизической установки Токамак КТМ162                        |

| 4.1.1. Разработка устройства исправления ошибок                   |

| 4.1.2. Работа устройства исправления ошибок                       |

| 4.2. Проверка работы устройств декодирования на                   |

| экспериментальном стенде                                          |

| 4.2.1. Описание эксперимента                                      |

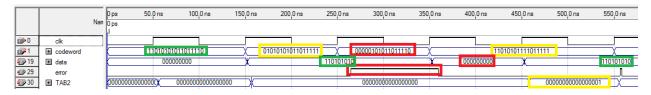

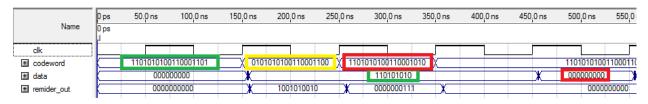

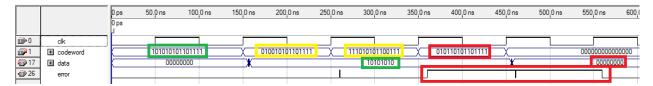

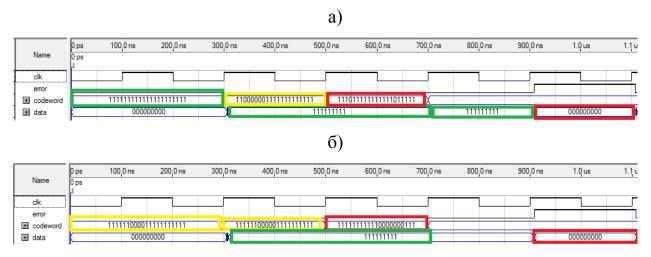

| 4.2.2. Исправление двукратной независимой ошибки с                |

| применением ЦПК (17,9,5)                                          |

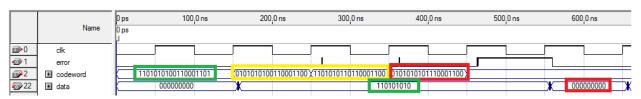

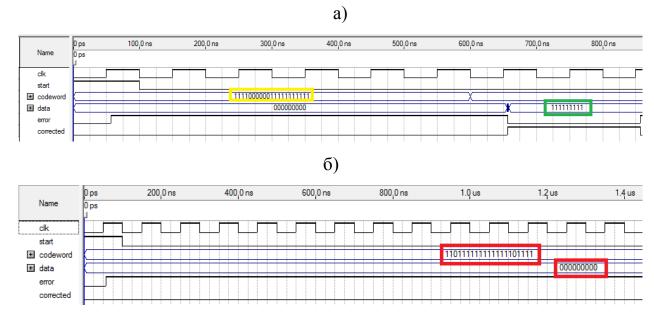

| 4.2.3. Исправление пакетной ошибки с применением ЦПК                         |

|------------------------------------------------------------------------------|

| (15,8,3)                                                                     |

| 4.3. Основные результаты и выводы по главе                                   |

| ЗАКЛЮЧЕНИЕ                                                                   |

| СПИСОК ЛИТЕРАТУРЫ                                                            |

| ПРИЛОЖЕНИЕ А. Блок-схемы алгоритмов вычисления контрольной суммы             |

| CRC8 для микроконтроллера Attiny 44                                          |

| ПРИЛОЖЕНИЕ Б. Шаблоны ошибок для табличного алгоритма                        |

| декодирования                                                                |

| ПРИЛОЖЕНИЕ В . Количество тактов, необходимых для исправления                |

| шаблонов ошибок для помехоустойчивых кодов $(17,9,5)$ и БЧХ $(19,9,5)$ $209$ |

| ПРИЛОЖЕНИЕ Г. Копии свидетельств о регистрации программ для ЭВМ 212          |

| ПРИЛОЖЕНИЕ Д. Копии актов внедрения результатов диссертационного             |

| исследования                                                                 |

# ПЕРЕЧЕНЬ ИСПОЛЬЗУЕМЫХ СОКРАЩЕНИЙ

ПЛИС – программируемая логическая интегральная схема.

МК – микроконтроллер.

CRC – cyclic redundancy code.

КС – кодовое слово.

ПК – помехоустойчивый код.

ЦПК – циклический помехоустойчивый код.

коды БЧХ – коды Боуза-Чоудхури-Хоквингема.

коды РС – коды Рида-Соломона.

БМА – алгоритм Берлекэмпа-Месси.

ПО – программное обеспечение.

ЭВМ – электронная вычислительная машина.

САПР – система автоматизированного проектирования.

ЛМС – локальный модуль синхронизации.

ЦБС – центральный блок синхронизации.

ВУ – вычислительные устройства.

код БЧХ (15, 7, 5) — код Боуза-Чоудхури-Хоквингема с длиной кодового слова 15 бит, длиной информационного блока 7 бит и расстоянием Хэмминга равным 5.

код PC (7, 3) – код Рида-Соломона с длиной кодового слова 7 символов и длиной информационного блока 3 символа.

### **ВВЕДЕНИЕ**

### Актуальность работы

В настоящее время в эпоху цифровой передачи данных актуальным является обеспечение целостности передаваемых данных ОТ одного вычислительного устройства (ВУ) к другому. Каналы передачи данных могут быть ненадежными в виду воздействия различных шумов и наводок. В свою очередь, в вычислительных устройствах при передаче информации от одного блока к другому любая одиночная ошибка может существенно нарушить процесс вычислений или привести к снижению производительности ВУ. Искажения в данных или командах, возникающие в процессе передачи между элементами вычислительной техники, также обуславливаются старением элементов, ухудшением качества электрических соединений и нестабильностью питания. Из-за отказа отдельных интегральных схем ошибки возникают и при хранении данных, поэтому большая часть ошибок, как правило, приходится на память. Таким образом, при проектировании устройств передачи (приёма), а также хранения информации требуется реализация способов и алгоритмов обнаружения и исправления ошибок, возникающих в результате воздействия помех или сбоев оборудования.

Одним из известных подходов к обнаружению и исправлению ошибок является применение помехоустойчивого кодирования с избыточностью кода [1–7].

Первые классы кодов, исправляющие одиночные ошибки, были введены Р. Хэммингом [1] в 1956 году. В 60-х годах XX века Р. Боуз [2], Д. Рой-Чоудхури [2], А. Хоквингем [3] (коды Боуза-Чоудхури Хоквингема, БЧХ), И. Рид [4] и Г. Соломон [5] (коды Рида-Соломона, РС) предложили более сильные коды, исправляющие многократные ошибки. Такие коды используются в системах управления, связи и устройствах вычислительной техники по сей день. Из российских ученых большой вклад в исследование помехоустойчивых кодов внесли Харкевич А.А., Колесников В.Д., Золотарёв В.В., Зяблов В.В. В

процессе развития вычислительной техники предложенные алгоритмы исправления ошибок нашли применение в различных устройствах передачи и хранения данных.

После открытия мощных кодов, исправляющих многократные ошибки, актуальной стала задача разработки эффективных способов и алгоритмов их декодирования. Первые алгоритмы построения И ДЛЯ построения декодирования кодов БЧХ и Рида-Соломона с практическим применением были предложены У. Питерсоном [6] и Э. Берлекэмпом [7]. В современных научных трудах можно встретить исследования способов декодирования различных помехоустойчивых кодов таких российских ученых как Золотарев В.В. [8–11] (многопороговые декодеры), Гладких А.А. [12–15] (декодирование избыточных С.И. блоковых кодов), Егоров [16–19] (декодеры низкоплотностных кодов и кодов Рида-Соломона), Башкиров А.В. [20–22] многофункциональных (реализация декодеров на программируемых логических интегральных схемах (ПЛИС)).

В 1961 году У. Питерсоном был предложен отдельный вид помехоустойчивых кодов, позволяющих обнаруживать ошибки без прямого исправления – циклический избыточный код CRC (Cyclic redundancy code) [23]. Основной целью кодов CRC было эффективное обнаружение ошибок с применением наименьшей и фиксированной избыточности. Исправление ошибок на основе таких кодов осуществляется за счёт повторной передачи пакетов данных.

На данный момент CRC-коды длиной от 4 до 64 бит (CRC4, CRC8, CRC16, CRC32, CRC64) применяются в протоколах передачи данных ETHERNET, ZigBee, ModBus, DLMS/SLIP, а также в архиваторах WinRaR, WinZIP. В сетевых платах ЭВМ проверка целостности данных с применением CRC-кодов аппаратно реализуются в составе модуля FCS (Frame check sequence) [24, 25]. Помехоустойчивые коды, исправляющие ошибки, широко применяются в стандартах цифрового телевизионного вещания DVB-T2 [26],

системах спутниковой [27, 28], сотовой связи [29], системах автоматизации [30],производства И телекоммуникациях системах дистанционного Земли [31]. Применение зондирования помехоустойчивых кодов, обнаруживающих и исправляющих ошибки, является одним из способов повышения надежности цифровых и запоминающих устройств ЭВМ [32–37]. Современные модули памяти SDRAM DDR реализуются с аппаратной поддержкой алгоритмов исправления ошибок на основе кодов Хэмминга и дополнительных модулей хранения кодов ECC (Error-correcting code) [38–40].

Существующие алгоритмы обнаружения ошибок, применяемые устройствах с контролем целостности данных и основанные на применении циклических избыточных кодов, позволяют эффективно обнаруживать ошибки в больших пакетах данных, однако либо обладают низким быстродействием (классический побитовый алгоритм), либо при модификации требуется достаточно большой объем памяти (табличный алгоритм). Таким образом, актуальной является задача разработки алгоритма вычисления циклических избыточных который будет компромиссным кодов, вариантом ПО быстродействию и аппаратным затратам при реализации на микроконтроллерах и ПЛИС.

Циклические помехоустойчивые коды (ЦПК) БЧХ, исправляющие независимые ошибки, обычно записываются в формате (n, m, d), где n - длина кодового слова, m — длина информационного блока, d — расстояние Хэмминга [1]. Например, ЦПК БЧХ (15, 7, 5) имеет длину кодового слова 15 бит, длину информационного блока 7 бит и расстояние Хэмминга равное 5. Длины кодовых слов таких кодов ограничены выражением  $n=2^h$  - 1, где h натуральное число. Данный факт не позволяет построить помехоустойчивый код для любых n и m без применения операции укорачивания, что приводит к снижению эффективности кода. также К низкой эффективности использования аппаратных ресурсов при разработке устройств исправления ошибок. Коды Рида-Соломона, являющиеся частным случаем кодов БЧХ,

имеют меньшую избыточность, но при этом ориентированы на исправление только пакетных ошибок. Для реализации существующих алгоритмов декодирования помехоустойчивых кодов БЧХ и Рида-Соломона требуется знание арифметики полей Галуа и решение ключевых уравнений, что увеличивает сложность разработки устройств исправления ошибок. Таким место проблема построения образом, помехоустойчивых имеет кодов, аналогичных кодам БЧХ и Рида-Соломона, но более эффективных по избыточности и для любых длин информационного сообщения без применения операции укорачивания.

Во многих системах с защитой передаваемых данных от ошибок модули обнаружения и исправления ошибок являются служебными (вспомогательными), а основные ресурсы памяти и вычислительные мощности устройств используются для решения задач согласно прямому назначению системы. В связи с этим, сформулируем следующие требования к способам, алгоритмам и устройствам, обеспечивающим целостность информации:

- высокая эффективность наилучшее отношение полезной информации к избыточной;

- простота реализации низкая сложность алгоритмов, а также наименьшая область знаний для программных и аппаратных реализаций;

- быстродействие минимальное время (количество тактов устройства) для обнаружения и исправления ошибок;

- минимальные аппаратные затраты наименьшее количество логических элементов модуля исправления ошибок и небольшой требуемый объем памяти запоминающего устройства для реализации в системах с дефицитом ресурсов.

Таким образом, актуальными задачами являются разработка программ и аппаратная реализации устройств обнаружения и исправления ошибок, удовлетворяющих сформулированным ранее требованиям с применением

новых и модификацией существующих алгоритмов. С учетом описанных выше проблем и задач сформулируем цель настоящей работы.

**Целью** работы является разработка эффективных алгоритмов, программ и устройств обнаружения и исправления пакетных или независимых ошибок при передаче и хранении данных с информационным сообщением короткой длины.

Для выполнения поставленной цели необходимо выполнить следующие задачи:

- 1. Провести обзор и анализ существующих способов и алгоритмов обнаружения и исправления ошибок, применяемых в устройствах передачи и хранения данных.

- 2. Разработать алгоритм быстрого вычисления циклических избыточных кодов СКС для реализации на микроконтроллерах и ПЛИС. Реализовать разработанный алгоритм на микроконтроллере и ПЛИС для сравнения с существующими алгоритмами.

- 3. Разработать алгоритм поиска образующих полиномов, позволяющий находить полиномы, применяемые для построения более эффективных циклических помехоустойчивых кодов, чем коды БЧХ.

- 4. Разработать устройства исправления независимых ошибок на ПЛИС с использованием известных циклических помехоустойчивых кодов короткой длины и предложенного помехоустойчивого кода, построенного на основе результатов поиска образующего полинома, для сравнения быстродействия и аппаратных затрат.

- 5. Осуществить поиск образующих полиномов для построения циклических кодов, исправляющих пакетные ошибки. Разработать алгоритм и устройства исправления пакетных ошибок на ПЛИС на основе циклического помехоустойчивого кода, исправляющего пакетные ошибки.

**Объектом исследования** являются программы и устройства на ПЛИС для обнаружения и исправления пакетных или независимых ошибок.

**Предметом исследования** являются алгоритмы обнаружения и исправления пакетных или независимых ошибок для реализации на ПЛИС.

**Методы исследований.** Для достижения поставленной цели в работе применены методы компьютерного моделирования, разработки программ на языках программирования низкого и высокого уровней; основы цифровой схемотехники и разработки цифровых устройств с применением систем автоматизированного проектирования.

Достоверность и обоснованность предложенных алгоритмов, программ и аппаратных реализаций подтверждается результатами экспериментальных исследований, компьютерным моделированием в САПР Quartus II и публикациями основных результатов работы в ведущих российских изданиях и трудах зарубежных конференций.

Научную новизну полученных в работе результатов определяют:

- 1. Матричный алгоритм вычисления контрольной суммы CRC, отличающийся от известных лучшим быстродействием при реализации на ПЛИС и меньшим требуемым объёмом памяти при программной реализации.

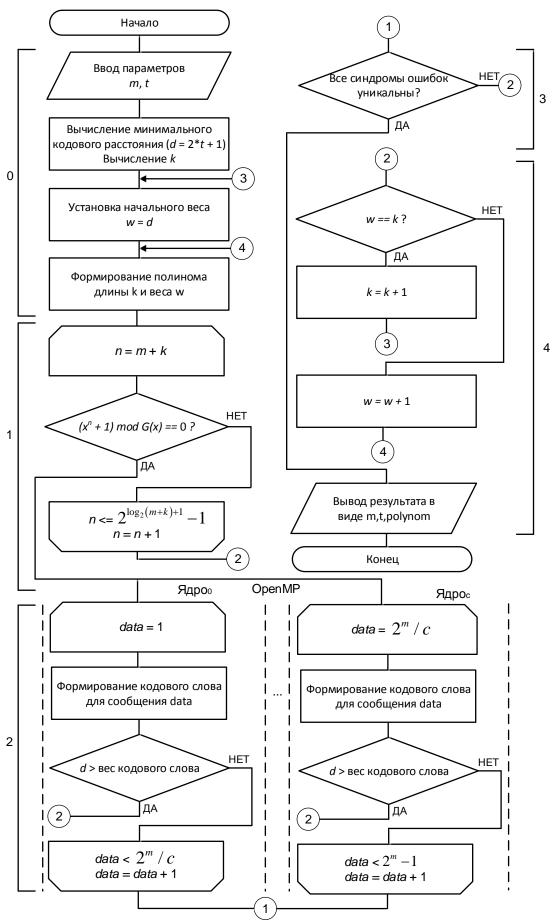

- 2. Алгоритм поиска образующих полиномов, адаптированный для параллельных вычислений и отличающийся от известных тем, что позволяет получать полиномы более короткой длины для построения циклических помехоустойчивых кодов, более эффективных с точки зрения отношения полезной информации к избыточной, чем коды БЧХ.

- 3. Предложенные быстродействующие декодирующие устройства на основе циклического помехоустойчивого кода (17, 9, 5) с меньшими аппаратными затратами, чем устройства на основе укороченного кода БЧХ (19, 9, 5).

- 4. Предложенная модификация циклического алгоритма декодирования с применением образующих полиномов, полученных с помощью программы поиска, позволяющая исправлять пакетные ошибки для циклических помехоустойчивых кодов без ограничения длины кодового слова.

### Практическая значимость работы

Практически значимыми являются программы вычисления контрольной суммы CRC с применением предложенного алгоритма, аппаратные реализации устройств вычисления CRC8 и CRC32 на ПЛИС, программы вычисления CRC8 на языке Assembler для микроконтроллера ATtiny44, алгоритмы и программы поиска образующих полиномов на языке С++ с применением технологии OpenMP. Разработанные устройства исправления независимых и пакетных ошибок на ПЛИС с применением табличного и циклического алгоритмов обеспечивают декодирования целостность информации устройствах По получено вычислительной техники. результатам исследований свидетельства о регистрации программы для ЭВМ.

Работа выполнена в рамках ФЦП «Исследования и разработки по приоритетным направлениям развития научно-технологического комплекса России на 2014—2020 годы», соглашение № 05.578.21.0272 от 20.12.2018 г. RFMEFI57818X0272) (уникальный идентификатор проекта ПО теме: «Разработка технических решений и аппаратно-программного комплекса цифровыми электрическими управления подстанциями ДЛЯ построения интеллектуальной энергосистемы» и хозяйственного договора № 4-673/16У от 26.09.2016 «Разработка средств технического обеспечения устройств сбора данных, контроля и защиты электрофизической установки токамак» (заказчик ООО «ТомИУС-проект», г. Томск).

## Реализация и внедрение результатов работы

Полученные алгоритмы и аппаратные модули на ПЛИС применены в системе управления электрофизической установки Токамак КТМ (Национальный ядерный центр, Республика Казахстан, г. Курчатов), в том числе разработанное устройство на ПЛИС для исправления пакетных ошибок длиной до 3 бит при длине сообщения 8 бит с модулем вычисления СRС8 в системе передачи команд от центрального блока подсистемы синхронизации к локальным модулям синхронизации.

Отдельные результаты диссертационного исследования использованы в учебном процессе НИ ТПУ в дисциплинах «Микропроцессоры и микроконтроллеры», «Программирование на языках описания аппаратуры».

### Основные положения, выносимые на защиту:

- 1. Матричный алгоритм вычисления циклических избыточных кодов CRC позволяет при программной реализации задействовать до 32 раз меньший объем памяти для хранения предвычисленных значений, а при аппаратной реализации на ПЛИС увеличить быстродействие устройств вычисления CRC до 8,5 раз по сравнению с табличным алгоритмом.

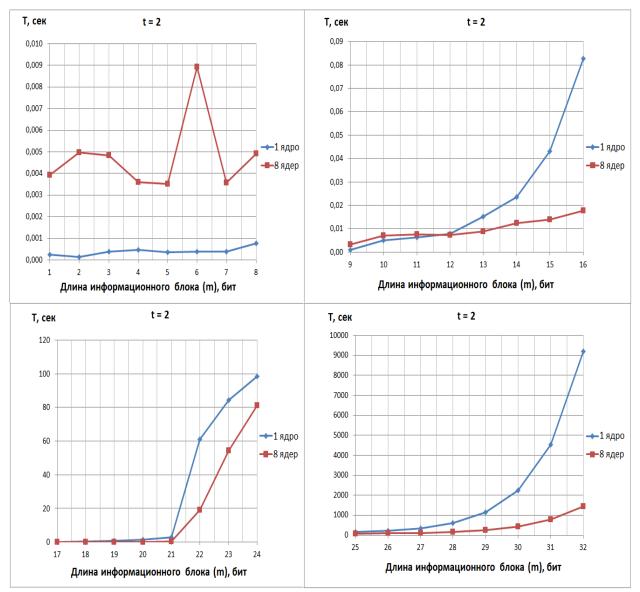

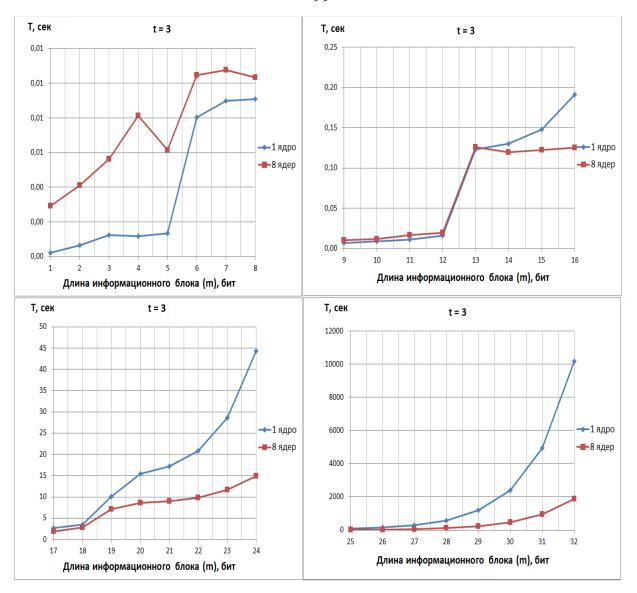

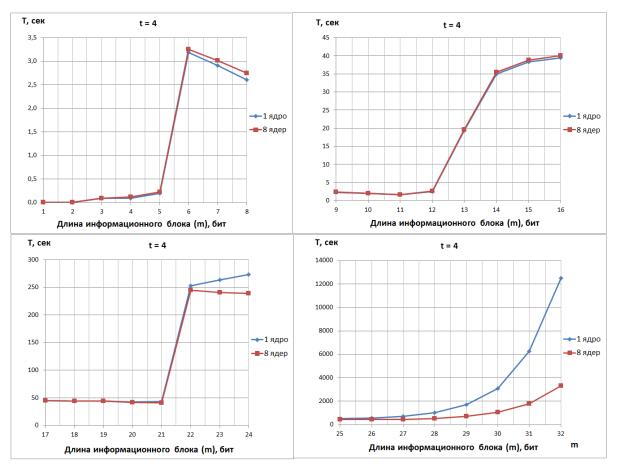

- 2. Алгоритм поиска образующих полиномов, адаптированный для параллельных вычислений, позволяет находить полиномы для построения циклических помехоустойчивых кодов, имеющих избыточность до 25 % меньше, чем у циклических кодов БЧХ с сообщением длиной от 2 до 32 бит и количеством исправляемых ошибок от 2 до 4.

- 3. Разработанное устройство исправления независимых ошибок на ПЛИС с применением циклического помехоустойчивого кода (17, 9, 5) на основе циклического алгоритма декодирования обладает в 2 раза лучшим быстродействием и позволяет повысить эффективность использования логических элементов в 2,6 раза по сравнению с устройством на основе укороченного кода БЧХ (19, 9, 5) с аналогичной длиной информационного блока.

- 4. Разработанное устройство исправления пакетных ошибок на ПЛИС с применением модифицированного циклического алгоритма декодирования и образующих полиномов, полученных с помощью программы поиска, позволяет исправлять пакетные ошибки для циклических помехоустойчивых кодов без ограничения длины кодового слова.

## Соответствие результатов паспорту научной специальности

В работе приведены результаты создания принципиально новых схем и устройств с применением языка описания аппаратуры для решения задачи

контроля целостности информации, передаваемой между элементами вычислительной техники, что соответствует п.1 паспорта научной специальности 05.13.05 Элементы и устройства вычислительной техники и систем управления. В соответствие с п.4. паспорта научной специальности разработаны алгоритмы и программы контроля целостности данных в устройствах вычислительной техники.

**Апробация работы.** Основные результаты работы обсуждались на следующих конференциях и семинарах:

Международная конференция научно-практическая «Молодежь современные информационные технологии» (г. Томск, 2012 – 2017 гг.), Международная научно-практическая конференция студентов, аспирантов и молодых учёных «Современные техника и технологии» (г. Томск, 2012, 2014 гг.), 9-й Международный Форум по Стратегическим Технологиям 2014, IFOST-2014 (г. Дакка, Бангладеш, 2014 г.), XII Международная IEEE Сибирская конференция по управлению и связи, SIBCON-2016 (г. Москва, 2016 г.), III Международная научная конференция «Информационные технологии в науке, управлении, социальной сфере и медицине» (г. Томск, 2016 г.), 55-ой конференция Международная научная студенческая MHCK-2017, Новосибирск, 2017 г), Международная научно-техническая конференция студентов, аспирантов и молодых ученых, посвященная 55-летию ТУСУРа, «Научная сессия ТУСУР-2017» (г. Томск, 2017 г.), III Всероссийский молодежный научный форум «Наука будущего – наука молодых», (г. Нижний новгород, 2017 г), Всероссийская научная конференция молодых ученых Инновации», (г. Новосибирск, 2017 «Наука. Технологии. Международная научно-практическая конференция «Высокопроизводительные вычислительные системы И технологии научных исследованиях, автоматизации управления и производства», BBCT-2018 (г. Барнаул, 2018 г.).

Результаты диссертационной работы были отмечены медалью Российской академии наук в области информатики, вычислительной техники и автоматизации за научно-исследовательскую работу «Исследования матричного алгоритма вычисления контрольной суммы CRC и его аппаратная реализация» по итогам конкурса 2014 г (постановление Президиума РАН № 24 от 17.02.2015 г.).

### Публикации

Результаты диссертационного исследования опубликованы в 6 статьях рецензируемых изданий, рекомендованных ВАК РФ. Четыре публикации индексированы в Международной базе данных SCOPUS (Conference paper) и 6 публикаций – в Web of Science (Conference paper). Получено 4 свидетельства о регистрации программы для ЭВМ.

### Личный вклад

Основные научные результаты, выносимые на защиту, получены автором самостоятельно. В работах, опубликованных в соавторстве, личный вклад состоит в следующем: в публикациях [58 – 61, 64, 65, 70, 71, 73] автором реализован на ПЛИС, микроконтроллере и под ОС Linux матричный алгоритм вычисления контрольной суммы CRC. В работах [86-91, 95, 96] автором предложены и реализованы алгоритмы поиска образующих полиномов для построения циклических помехоустойчивых кодов, исправляющих независимые и пакетные ошибки. Поставлены компьютерные эксперименты по поиску образующих полиномов с применением технологий параллельных вычислений. В публикациях [103–107] автором проведены исследования аппаратных реализаций на ПЛИС циклического алгоритма декодирования на примере кодов БЧХ короткой длины (до 15 бит). В работах [97, 117, 118] автором предложены и реализованы устройства исправления ошибок на основе циклического помехоустойчивого кода (17, 9, 5), обладающего лучшими характеристиками по сравнению с кодом БЧХ (15, 7, 5) и укороченным кодом БЧХ (19, 9, 5). Предложенный автором циклический алгоритм декодирования и устройство на ПЛИС для исправления пакетных ошибок представлены в работах [69, 99 – 101].

Структура и объём работы. Диссертация состоит из введения, четырех глав, заключения, списка литературы из 121 наименования и пяти приложений. Объём диссертации составляет 217 страниц, включая 102 рисунка и 40 таблиц.

**Первая глава** посвящена анализу современных способов и алгоритмов обнаружения и исправления пакетных и независимых ошибок при передаче и хранении данных.

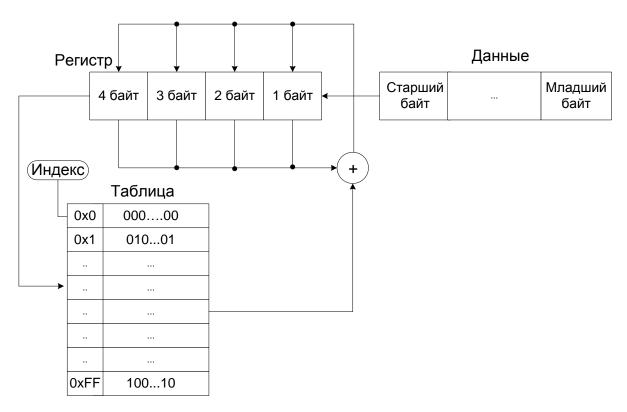

Рассмотрены известные алгоритмы вычисления циклических избыточных кодов CRC. Анализ показал, что существуют два основных алгоритма вычисления CRC: классический с применением последовательного сдвига бит данных через регистр и операции сложения по модулю 2 (Исключающее ИЛИ), а также табличный, ускоряющий процесс вычисления CRC за счет применения таблицы предвычисленных значений. Недостатком первого алгоритма является низкая скорость вычисления из-за побитового сдвига. Недостатком табличного алгоритма является то, что требуемый объем памяти для хранения таблицы предвычисленных значений (256 байт для CRC8, 1 Кб для CRC32) превышает объем памяти программ для исходного кода вычисления CRC.

Проанализированы существующие способы и алгоритмы исправления пакетных и независимых ошибок при передаче данных. Обозначена проблема выбора образующего полинома, позволяющего строить эффективные помехоустойчивые коды, исправляющие как независимые, так и пакетные ошибки, а также алгоритма декодирования данных кодов, требующего минимальных аппаратных и вычислительных затрат для его реализации.

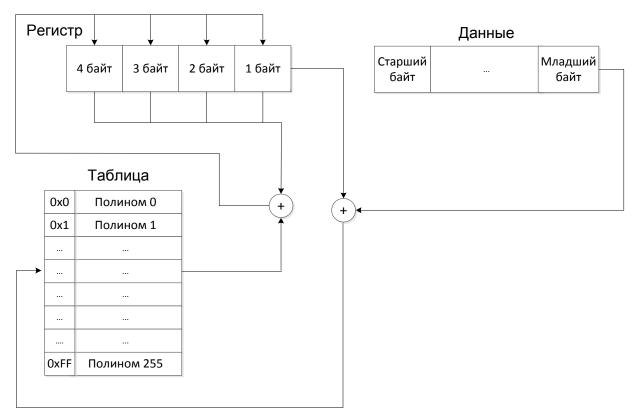

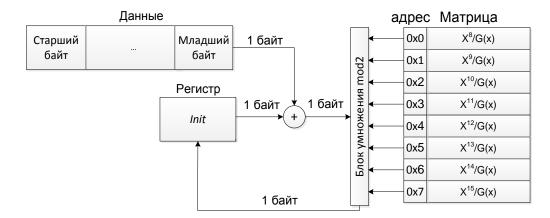

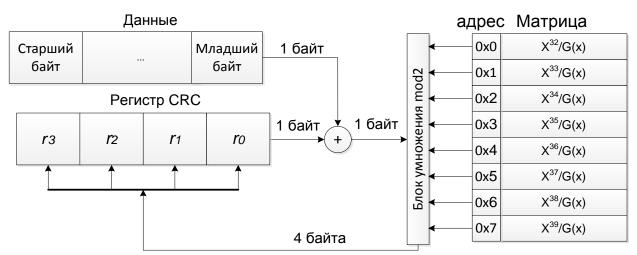

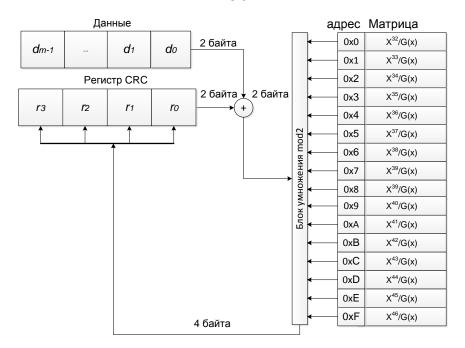

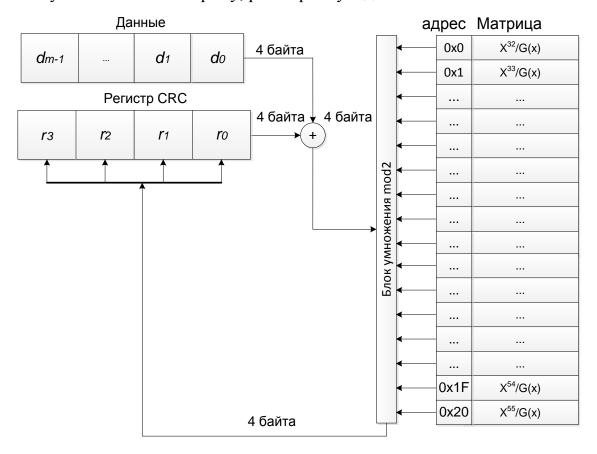

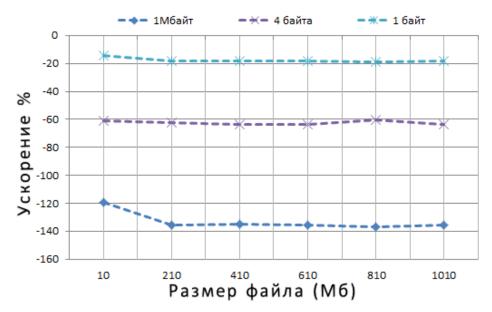

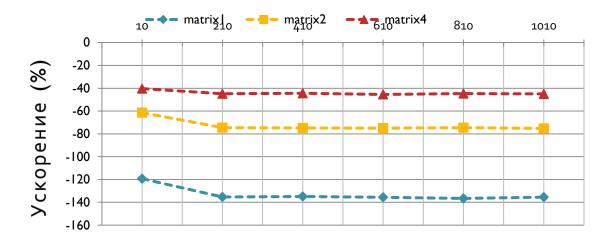

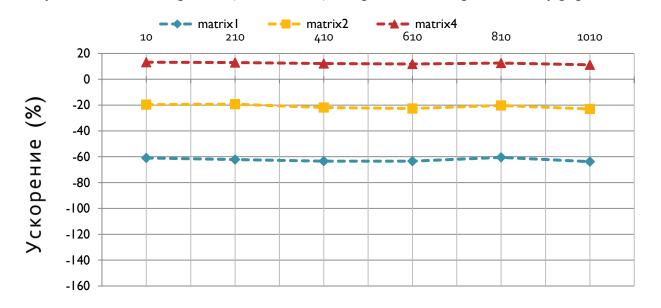

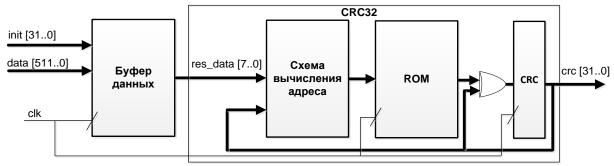

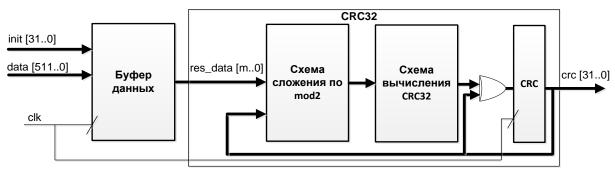

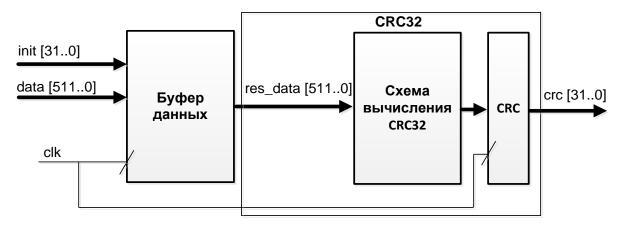

Во **второй** главе предложен матричный алгоритм вычисления контрольной суммы CRC с модификациями, позволяющими увеличить размер блока данных, обрабатываемого за итерацию. Поставлен компьютерный эксперимент по вычислению контрольной суммы CRC32 для различных данных объёмом от 10 до 1010 Мб. Установлено, что реализация матричного алгоритма со сдвигом и буфером, равным 4 байта, является более

быстродействующей, чем реализация табличного алгоритма. Установлено, что для данной матричной реализации требуется в 8 раз меньший объем памяти.

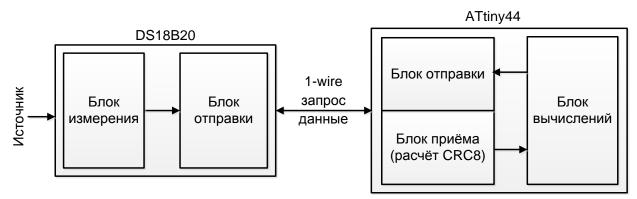

Поставлен эксперимент на микроконтроллере Attiny44 по вычислению контрольной суммы CRC8 для системы измерения температуры с применением датчика DS18B20. По результатам эксперимента выработаны рекомендации к применению алгоритмов расчёта CRC для систем с дефицитом ресурсов — небольшим объёмом памяти программ и данных и низкой производительностью.

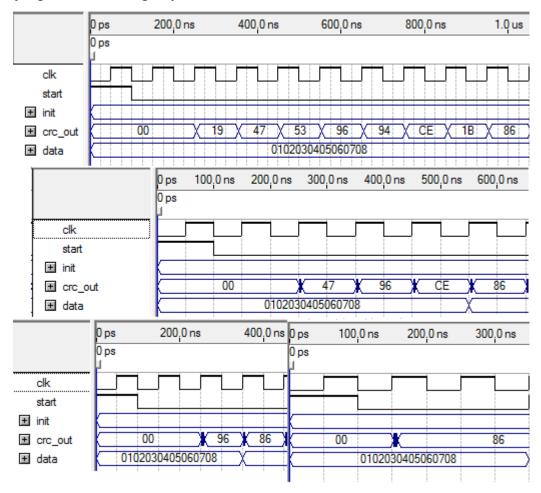

Поставлен эксперимент по вычислению CRC8 и CRC32 на ПЛИС Cyclone III от Altera. Результаты экспериментов показали, что увеличение размера блока данных, обрабатываемого за итерацию матричным алгоритмом, позволяет увеличить быстродействие устройства вычисления CRC, однако при этом увеличивается количество логических элементов ПЛИС. Установлено, что в отличие от микроконтроллерной реализации, где вычисления производятся строго последовательно по тактовому сигналу, архитектура ПЛИС позволяет параллельно обрабатывать несколько байт данных, что хорошо подходит для реализации матричного алгоритма.

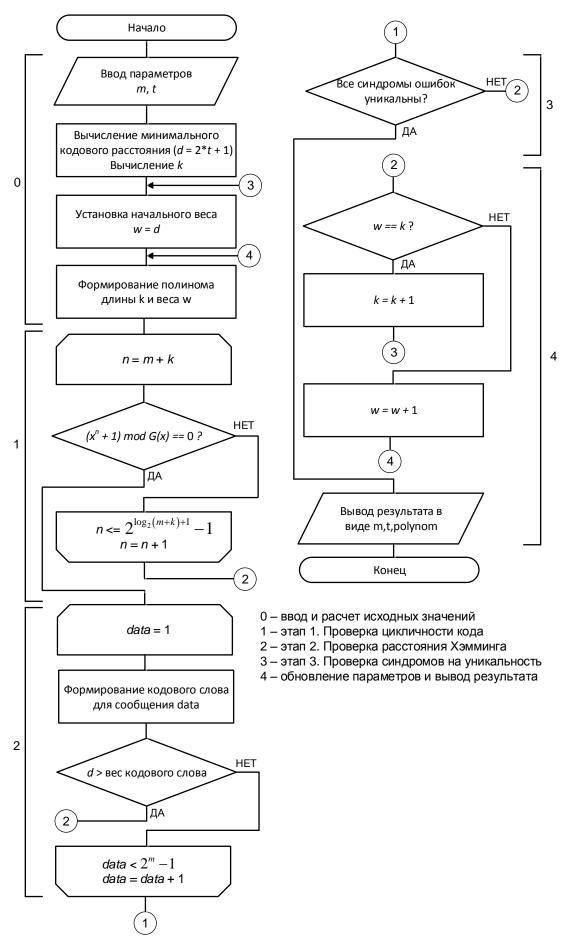

В третьей главе предложен алгоритм поиска образующих полиномов, отличающийся от известных тем, что позволяет находить полиномы для построения циклических помехоустойчивых кодов более эффективных по скорости кода, чем коды БЧХ.

Поставлен эксперимент образующих компьютерный ПО поиску полиномов с применением технологий параллельных вычислений исправляющих независимые построения кодов, И пакетные Разработанный алгоритм поиска позволяет находить полиномы для построения кодов, длина которых на 1–5 бит короче, чем коды БЧХ при длине информационного блока до 32 бит и кратности исправляемых ошибок до 4..

Поставлен эксперимент по исправлению независимых и пакетных ошибок на микроконтроллере Atmega8515 циклическим и табличным алгоритмами

декодирования. По результатам эксперимента сформулированы рекомендации по применению исследуемых алгоритмов для исправления ошибок в микропроцессорных системах сбора данных и управления.

Проведено исследование аппаратных реализаций на ПЛИС декодеров помехоустойчивого кода БЧХ (15, 7, 5) с различными алгоритмами декодирования. Циклический алгоритм декодирования при реализации на ПЛИС обладает лучшим быстродействием по сравнению с известным алгоритмом Берлекэмпа-Месси, за счёт простых операций проверки веса остатка и сложений по модулю 2. При параллельной реализации на ПЛИС это требует наименьшего количества тактов.

Предложены устройства исправления независимых ошибок на ПЛИС на основе циклического помехоустойчивый кода (17, 9, 5), обладающего большей скоростью и позволяющего кодировать более длинный информационный блок при сохранении избыточности, чем код БЧХ (15, 7, 5). Проведено сравнение характеристик разработанных устройств исправление ошибок на ПЛИС с применением предложенного помехоустойчивого кода (17, 9, 5) и укороченного кода БЧХ (19, 9, 5). Сделаны выводы о том, что декодирующие устройства с (17,5) применением помехоустойчивого кода 9, являются более быстродействующими и менее аппаратно-затратными, чем устройства с применением укороченного кода БЧХ (19, 9, 5).

алгоритма Предложена модификация циклического декодирования, позволяющая исправлять пакетные ошибки с применением образующих полиномов, найденных с помощью алгоритма поиска для пакетных ошибок. Приведено описание и исследование разработанных декодеров циклического помехоустойчивого кода (15, 8, 3) на ПЛИС, исправляющих пакетные ошибки длиной до 3 бит с применением табличного и циклического алгоритмов декодирования. Установлено, обладают что декодеры лучшим быстродействием и меньшими аппаратными затратами, чем декодеры БЧХ кода (15, 7, 5) с аналогичной длиной кодового слова.

На примере устройства декодирования аналога кода РС (7, 3) с длиной сообщения 9 бит и длиной кодового слова 21 бит продемонстрирована возможность циклического алгоритма исправлять пакетные ошибки длиной до 6 бит.

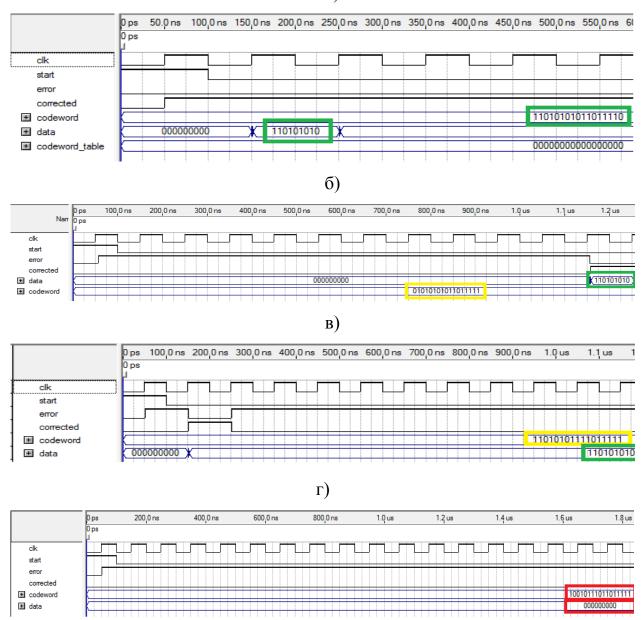

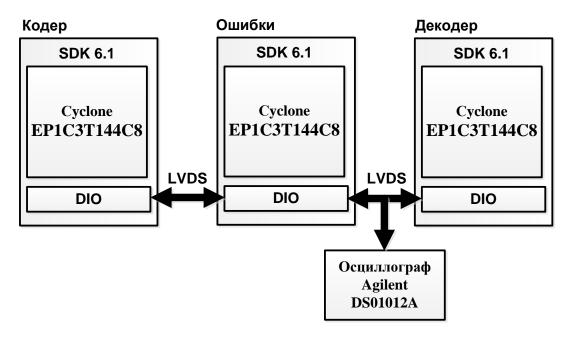

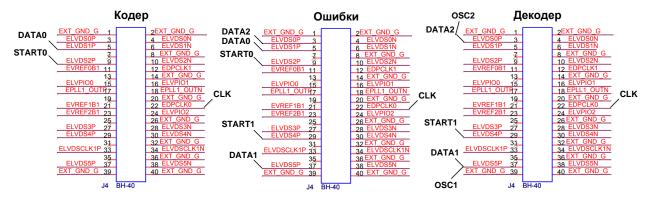

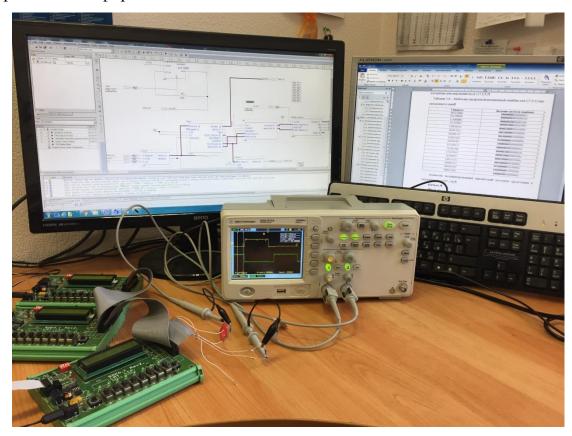

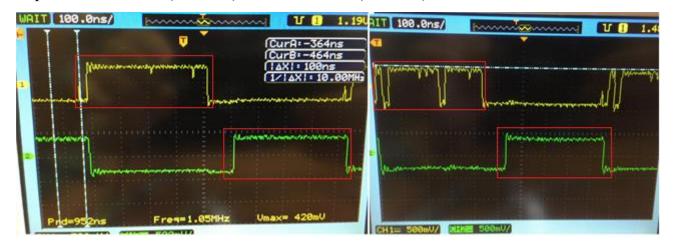

В четвёртой главе приведено описание практического применения устройств обнаружения и исправления пакетных ошибок с помехоустойчивым кодом (15, 8, 3) и циклическим избыточным кодом CRC8 для обеспечения целостности передаваемых команд подсистемы синхронизации системы электрофизической установки управления Токмак KTM. Представлены описание и результаты эксперимента по исправлению пакетных и независимых ошибок на специальном применением SDK-6.1 стенде с макетов осциллографа DS01012A.

В заключении приведены выводы и кратко описаны основные результаты диссертационной работы.

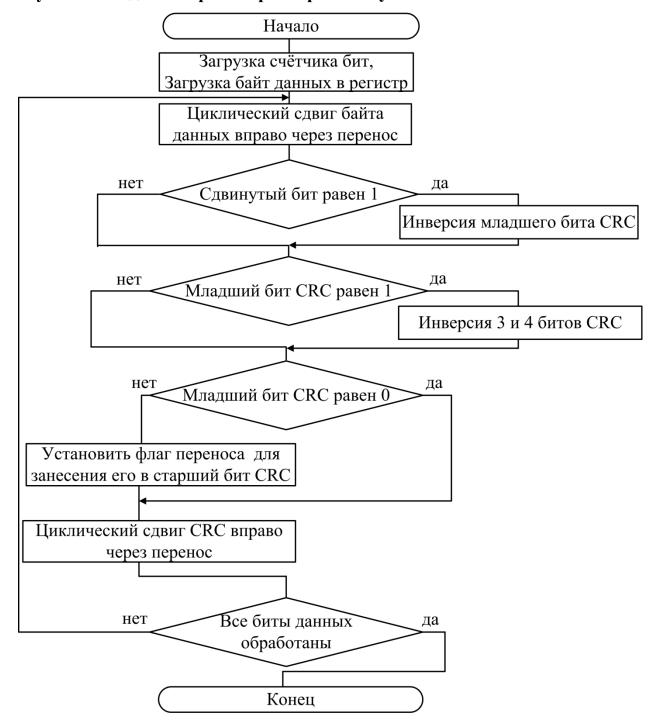

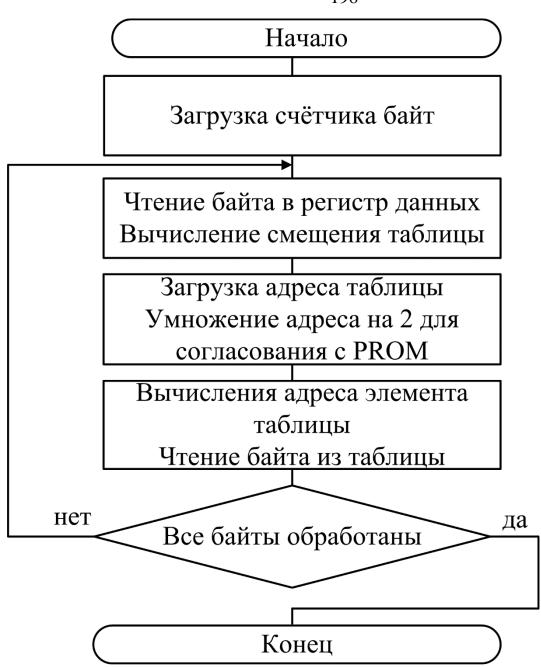

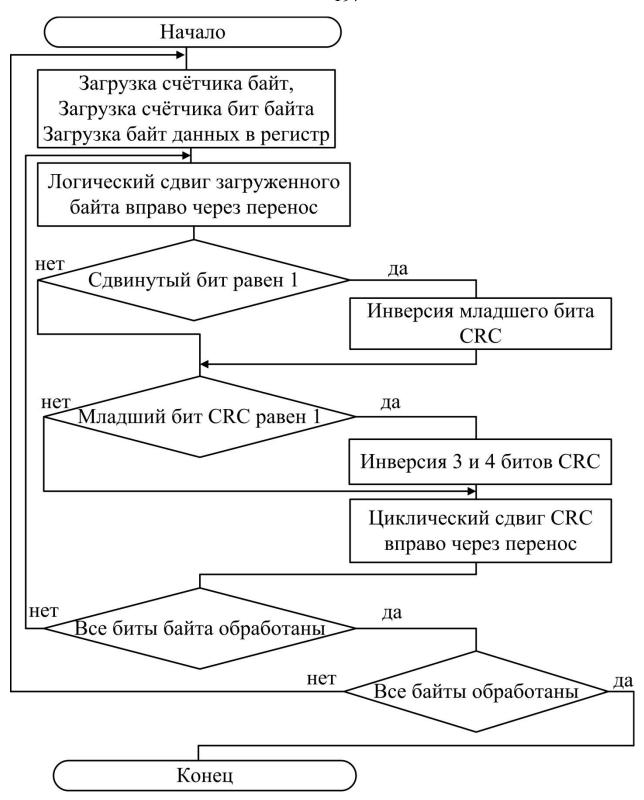

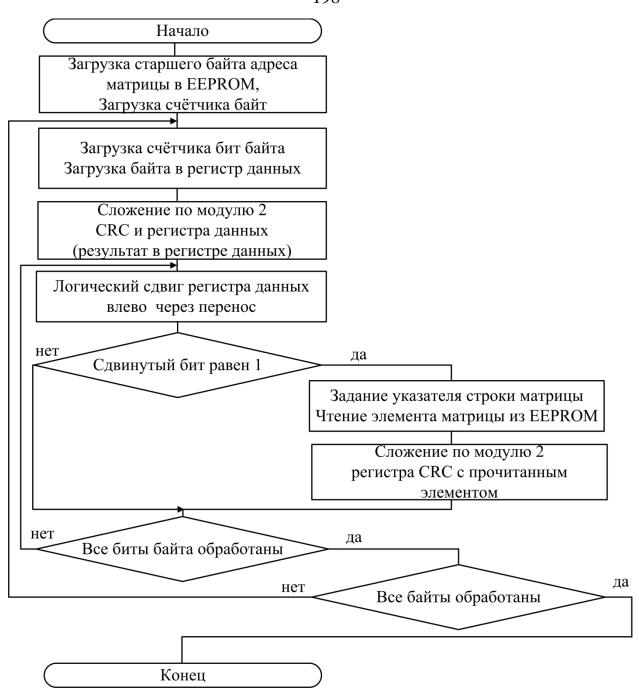

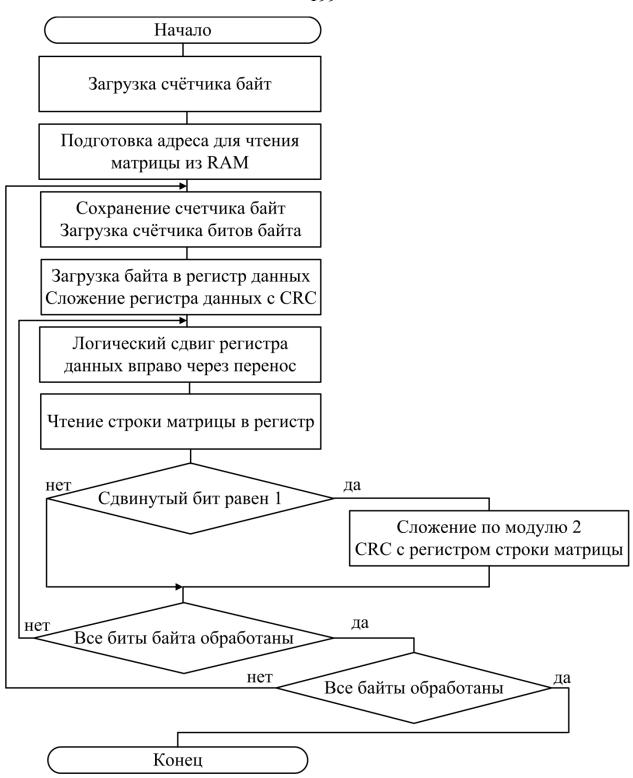

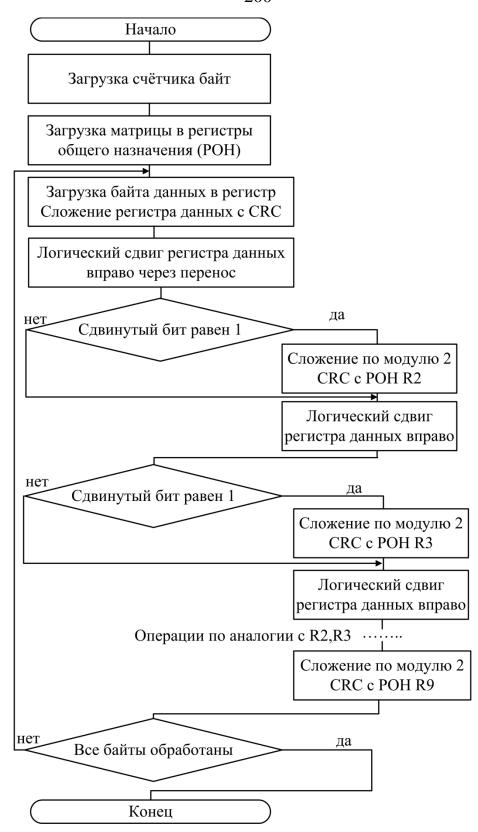

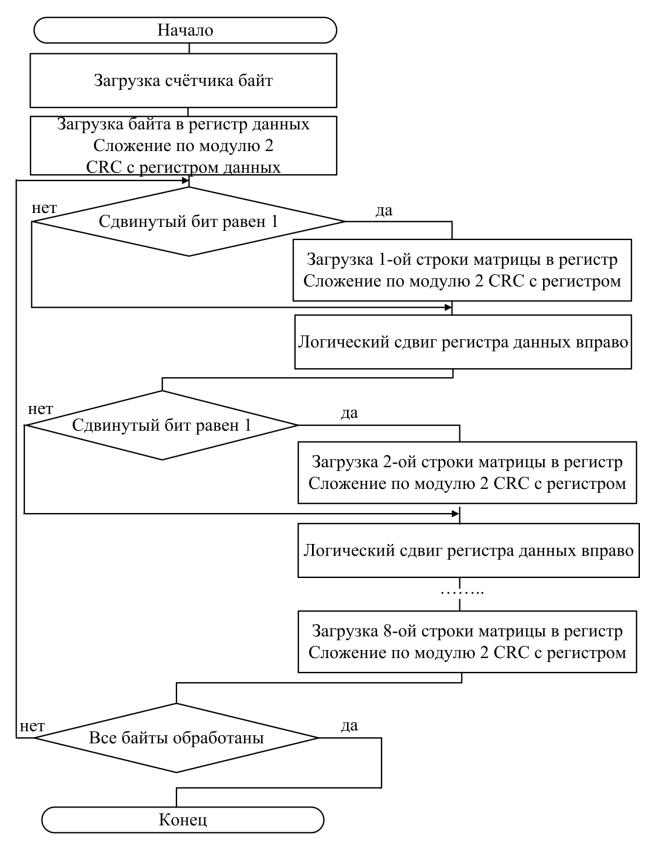

В **приложении А** приведены блок-схемы алгоритмов вычисления CRC8 для программной реализации на микроконтроллере, описанной в главе 2.

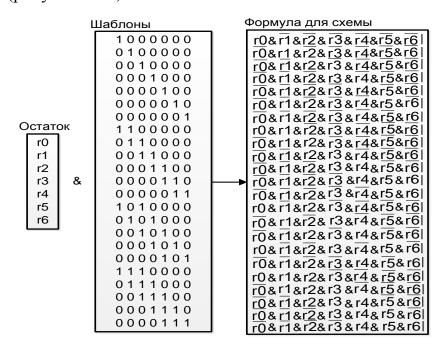

В приложении **Б** приведены таблицы шаблонов ошибок для помехоустойчивого кода БЧХ (15, 7, 5) и предложенного помехоустойчивого кода (17, 9, 5), описанных в главе 3.

В приложении В приведены таблицы, показывающие количество тактов, необходимое для исправления независимых ошибок для циклических помехоустойчивых кодов (17, 9, 5) и укороченного кода БЧХ (19, 9, 5) при классической реализации циклического алгоритма декодирования.

В **приложении** Г представлены копии свидетельств о регистрации программ для ЭВМ.

В приложении Д представлены копии актов о внедрении результатов диссертационной работы.

# ГЛАВА 1. АНАЛИЗ СПОСОБОВ И АЛГОРИТМОВ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ПАКЕТНЫХ ИЛИ НЕЗАВИСИМЫХ ОШИБОК

Способы и алгоритмы обнаружения и исправления ошибок являются важными элементами для обеспечения надежности цифровых устройств [33] вычислительной техники. При этом наиболее чувствительными к искажению информации являются запоминающие устройства, поэтому в вычислительной технике наибольшее внимание уделяется обнаружению и исправлению ошибок в различных микросхемах памяти [32–37].

Существует множество методов обнаружения или исправления ошибок разного типа в различных системах передачи или хранения данных [1–15]. В основе таких методов лежит помехоустойчивое кодирование, которое подразумевает изменение или дополнение исходных данных путём внесения дополнительной (избыточной) информации по определенному алгоритму. Теория помехоустойчивого кодирования базируется на результатах Шенноном [41, 42], исследований, проведенных Клодом который сформулировал теорему для дискретного канала с шумом. В данной главе рассмотрены классы существующих помехоустойчивых кодов, а также способы реализации операций декодирования этих кодов.

# 1.1. Классификация помехоустойчивых кодов

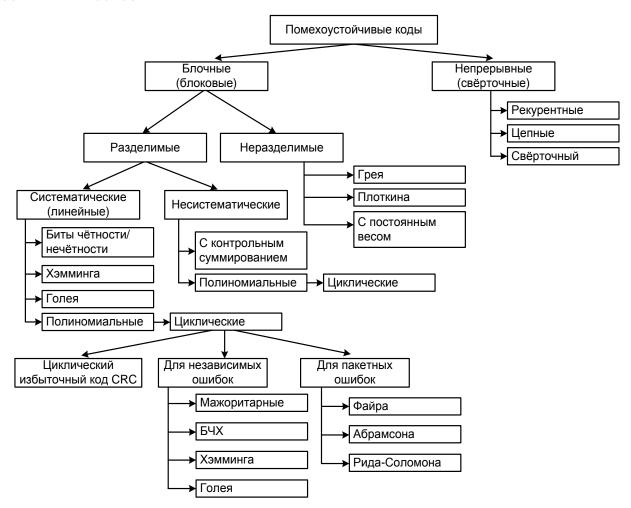

Помехоустойчивые коды можно разбить на две большие группы: блоковые и свёрточные [43]. В блоковых кодах кодирование и декодирование осуществляется пределах кодовой комбинации, каждый блок информационных символов обрабатывается отдельно. В свёрточных кодах обработка символов производится непрерывно, без разделения на блоки, и кодовая последовательность зависит от предыдущих, уже прошедших Ha 1.1 кодирование рисунке приведена классификация символов. помехоустойчивых кодов.

Блоковые коды бывают разделимыми и неразделимыми. При кодировании разделимыми кодами в выходных последовательностях символов

можно разграничить информационные символы и проверочные. В неразделимых кодах такое разграничение невозможно. В свою очередь, разделимые коды делятся на систематические и несистематические.

Рисунок 1.1 – Типы помехоустойчивых кодов

Систематические коды также называют линейными, так как в них контрольные (проверочные) разряды представляют собой различные линейные комбинации информационных разрядов. Линейные коды являются наиболее применяемыми на практике, поэтому существует большое количество видов кодов данного типа.

# 1.2. Коды для обнаружения ошибок

В сфере информационных технологий большую роль играют различные протоколы передачи и алгоритмы архивации данных. Одной из важных задач является контроль целостности данных при передаче по различным каналам

связи. Существует несколько способов обнаружения ошибок в процессе передачи (хранения) данных, отличающиеся количеством детектируемых ошибок, быстродействием, требуемыми программными и аппаратными ресурсами для реализации.

### 1.2.1. Контрольная сумма

Самый простой способ решения задачи обнаружение ошибок — вычисление некоторого опознавателя сообщения в виде контрольной суммы. Простейшим опознавателем достоверности переданного сообщения является бит контроля четности. Данный бит является суммой по модулю 2 всех бит сообщения, добавляется в конец сообщения и указывает на четность или нечетность единичных разрядов сообщения. Данный способ позволяет обнаружить ошибку нечётной кратности (1,3,5, и. т. д), требует минимальных аппаратных затрат, но снижает производительность системы передачи данных из-за побитового сложения информационных бит сообщения.

Существуют модификации метода контроля чётности, в которых вычисляется сумма по модулю 2 всех байтов пакета [44]. Однократные ошибки в таком методе обнаруживаются с вероятностью 100 %, двукратные — с вероятностью 88% [44]. Однако пакетные ошибки (искажения нескольких смежных битов) данным методом выявляются довольно плохо. Также существует метод, основанный на арифметической сумме всех байтов (или слов) пакета [45, 46]. В данном методе при ее вычислении отбрасываются старшие разряды для сохранения заданной разрядности контрольной суммы (обычно 8 или 16). Однократные ошибки обнаруживаются с вероятностью 100 %. Вероятность не обнаружения двукратных ошибок в наихудшем случае составляет приблизительно 3 % [44]. Это наблюдается, когда в каждом из 8 разрядов всех байт пакета или в каждом из 16 разрядов всех слов пакета соотношение нулей и единиц составляет 50/50. При этом двукратные ошибки не выявляются, когда в одном разряде вследствие ошибки один из битов из «0»

переходит в <1», а другой бит в этом же разряде из <1» переходит в <0», что не изменяет общей суммы [45].

### 1.2.2. Циклический избыточный код CRC

Более совершенным является способ обнаружения, основанный на вычислении некоторого значения фиксированной длины (4,8,16,32,64 бит), являющейся функцией сообщения. Передающее устройство вычисляет данное значение и добавляет его к передаваемому сообщению [46]. Структура последнего, как правило, имеет следующий вид:

<исходное неизмененное сообщение> <контрольная сумма>.

Для проверки целостности данных на приёмной стороне, используя тот же самый алгоритм, применяют одну из следующих методик:

- 1) осуществляется расчет контрольной суммы CRC принятого сообщения и сравнение результата с полученным значением CRC;

- 2) осуществляется расчет контрольной суммы CRC для всего сообщения вместе CRC и сравнение результата с нулевым значением.

В случаях несоответствия результатов полученному значению CRC (подход 1) либо нулевому значению (подход 2) осуществляется повторная пересылка данных.

СRС является практическим приложением теории помехоустойчивого кодирования и применяется в различных протоколах передачи данных (ETHERNET, ZigBee, USB, ModBus, DLMS/SLIP), стандартах MPEG-2, PNG и алгоритмах архивации данных (WinRaR, WinZIP). Аппаратно реализуется на микросхемах, входящих в состав сетевых плат [24, 25]. Под избыточностью подразумевается наличие дополнительного (контрольного) блока данных в передаваемом сообщении. Данный код, построение которого основано на математических свойствах циклического кода [47], позволяет гарантированно обнаруживать ошибки кратности d-1, где d- минимальное кодовое расстояние. Ошибки кратностью d и больше CRC обнаруживает с достаточно высокой вероятностью  $P_{06} = 1 - \frac{1}{2r}$ , где r- разрядность CRC в битах. Методика

вычисления CRC базируется на свойствах деления многочленов по модулю два. Значение CRC является остатком от деления по модулю два многочлена, соответствующего входным данным, на образующий многочлен [48], который выбирается в зависимости от протокола или стандарта передачи (архивации) данных.

Существуют CRC, различные виды отличающиеся разрядностью контрольного блока, такие как CRC4, CRC8, CRC16, CRC32, CRC64. При увеличении разрядности CRC уменьшаются вероятности «коллизий» (случаев, при которых для разных сообщений можно получить одинаковое значение CRC) и увеличивается кратность обнаруживаемых ошибок. Так, контрольная сумма CRC4 применяется в стандарте цифровых сетей ITU-T G.704, CRC8 – в стандарте телевещания DVB-S2, стандарте передачи данных Bluetooth, в цифровых датчиках температуры Dallas Semiconductor (шина 1-Wire), CRC16 – в промышленных протоколах ModBus и DLMS/SLIP для сетей АСУТП, CRC32 – в протоколах передачи данных Ethernet, ZigBee, CRC64 – в стандартах ECMA-182. Виды наиболее применяемых на практике контрольных сумм CRC приведены в таблице 1.1.

Таблица 1.1 – Контрольные суммы CRC с образующими полиномами

| Вид CRC               | Применение                                   | Образующий полином |  |  |  |

|-----------------------|----------------------------------------------|--------------------|--|--|--|

|                       |                                              | (hex)              |  |  |  |

| CRC4                  | ITU-T G.704                                  | 0x3                |  |  |  |

| CRC8                  | DVB-S2                                       | 0xD5               |  |  |  |

| CRC8-Bluetooth        | Bluetooth                                    | 0xA7               |  |  |  |

| CRC8-CCITT            | ITU-T I.432.1, (02/99), ATM<br>HEC, ISDN HEC | 0x07               |  |  |  |

| CRC8-<br>Dallas/Maxim | 1-Wire bus                                   | 0x31               |  |  |  |

| CRC8-DARC             | Data Radio Channel                           | 0x39               |  |  |  |

### Окончание таблицы 1.1

| CRC8-WCDMA     | mobile networks                                    | 0x9B               |  |  |

|----------------|----------------------------------------------------|--------------------|--|--|

| CRC16-CCITT    | X.25, XMODEM, Bluetooth, SLIP                      | 0x1021             |  |  |

| CRC16-IBM      | Modbus, USB, ANSI X3.28                            | 0x8005             |  |  |

| CRC16-Profibus | fieldbus networks                                  | 0x1DCF             |  |  |

| CRC32          | Ethernet, ZigBee, WinRaR, PKZIP, PNG, MPEG-2, SATA | 0x04C11DB7         |  |  |

| CRC64-ECMA     | ECMA-182                                           | 0x42F0E1EBA9EA3693 |  |  |

| CRC64-ISO      | ISO 3309 (HDLC)                                    | 0x000000000000001B |  |  |

### 1.2.3. Параметрическая модель CRC-алгоритма

Параметрическая модель CRC-алгоритма предложена австралийским ученым в области информатики Ross Williams [46] и подразумевает краткое описание основных параметров, применяемых в реализации алгоритмов вычисления CRC. Модель должна параметризировать алгоритм так, чтобы отражать поведение различных реальных алгоритмов и включает следующие параметры:

- Name имя, присвоенное данному алгоритму. Строковое значение.

- Width степень алгоритма (разрядность CRC), выраженная в битах.

- образующий Poly полином. Записывается как битовая последовательность, при этом старший бит опускается – он всегда равен  $x^{32}+x^{26}+x^{23}+x^{22}$ Например, многочлен единице.  $+x^{16}+x^{12}+x^{11}+x^{10}+x^8+x^7+x^5+x^4+x^2+x+1$ будет записан как 1001100000100011101101101111. Для удобства полученное двоичное представление записывают в шестнадцатеричной форме.

- Init исходное содержимое регистра CRC на момент запуска вычислений.

Указывается в шестнадцатеричной системе счисления. По умолчанию 0x0.

- RefIn (reflect in) логический параметр. Если он имеет значение «False» («Ложь»), то байты сообщения обрабатываются, начиная с 7-го бита, который считается наиболее значащим, а наименее значащим считается

- бит 0. Если параметр имеет значение «True» («Истина»), то каждый байт перед обработкой зеркально отражается.

- RefOut логический параметр. Если он имеет значение «False» («Ложь»), то конечное содержимое регистра сразу передается на стадию XorOut, в противном случае, когда параметр имеет значение «True» («Истина»), содержимое регистра зеркально отражается перед передачей на следующую стадию вычислений.

- XorOut значение, обозначаемое шестнадцатеричным числом, с разрядностью, равной Width. Комбинируется с конечным содержимым регистра (после стадии RefOut) прежде, чем будет получено окончательное значение контрольной суммы.

- Check данное поле служит контрольным значением, которое может быть использовано для проверки правильности реализации алгоритма.

Поле содержит контрольную сумму, рассчитанную для ASCII строки «123456789».

В таблице 1.2 приведен пример модели CRC-алгоритма.

Таблица 1.2 – Параметрическая модель CRC-алгоритма для Ethernet

| Name   | CRC32      |

|--------|------------|

| Width  | 32         |

| Poly   | 0x04C11DB7 |

| Init   | 0xFFFFFFF  |

| RefIn  | True       |

| RefOut | True       |

| XorOut | 0xFFFFFFF  |

| Check  | 0xCBF43926 |

Для одного и того же набора данных и образующего полинома можно получить разные значения контрольной суммы CRC, поэтому при программной или аппаратной реализациях алгоритмов необходимо указывать полную модель вычисления.

В настоящее время на практике применяются два основных алгоритма вычисления контрольной суммы CRC: классический (побитовый) и табличный.

Данные алгоритмы принципиально отличаются быстродействием, сложностью программной и аппаратной реализаций и требуемыми для реализации ресурсами (памяти программ и данных, логические элементы). Основная проблема в данном случае заключается в поиске наиболее компромиссного решения между медленным, но наименее аппаратно затратным классическим алгоритмом, и быстрым, но требовательным к ресурсам табличным алгоритмом.

Циклические избыточные коды, несмотря на малую избыточность, не позволяют непосредственно исправлять ошибки без запроса повторной передачи и применяются в системах передачи данных, в которых повторная либо многократная посылка одного и того же пакета данных допустима (Ethernet, MobBus, SLIP). В случаях, когда повторная передача данных не допустима или должна быть сведена к минимуму необходимо применять прямую коррекцию ошибок (FEC–Forward Error Correction) на основе помехоустойчивых кодов, исправляющих ошибки без запроса (либо с минимальной вероятностью запроса) на повторную передачу данных.

## 1.3. Коды для исправления пакетных или независимых ошибок

Для обеспечения целостности данных в процессе передачи (хранения) без повторной передачи одного и того же блока данных применяют прямую коррекцию ошибок на основе помехоустойчивых кодов. Известно большое количество помехоустойчивых кодов, отличающихся структурой, функциональным назначением, энергетической эффективностью, алгоритмами кодирования и декодирования.

## 1.3.1. Систематические помехоустойчивые коды

#### Колы Хэмминга

Код Хэмминга позволяет исправлять однократные и обнаруживать двукратные ошибки [1]. Идея кодов Хемминга заключается в разбиении данных на блоки фиксированной длины и вводе в эти блоки контрольных (избыточных) бит, дополняющих до четности несколько пересекающихся групп,

охватывающих все биты блока. Количество контрольных разрядов k для исправления всех однократных ошибок кодового слова длины n=m+k. рассчитывается по формуле

$$k=2^k-m-1$$

, (1.1)

где m — длина информационного блока, k —длина контрольного блока.

(проверочные) Контрольные разряды размещаются среди информационных бит по позициям, равным степеням двойки. Каждый контрольный бит проверяет определенную группу информационных бит, при этом значения контрольного бита равно сумме по модулю два всех битов группы, которую он проверяет. Для определения контролируемых групп бит необходимо информационных разложить порядковые информационных бит по степени двойки. Так для сообщения длины m=8 бит код Хэмминга будет иметь вид, представленный на рисунке 1.2, где Кі – контрольный бит, Иі – информационный бит. При этом, согласно формуле (1.1), k = 4. Сверху над разрядами обозначены позиции разрядов в кодовом слове.

|            |            |    |    | 5  |    |    |            |    |    |    |    |

|------------|------------|----|----|----|----|----|------------|----|----|----|----|

| <b>K</b> 1 | <b>K</b> 2 | И1 | Кз | И2 | Из | И4 | <b>K</b> 4 | И5 | И6 | И7 | И8 |

Рисунок 1.2 – Формат кодового слова Хэмминга

Проверочные биты, которыми контролируются информационные, определяются следующим образом:

**И1:** поз.  $3 => 3 = 2^0 + 2^1 = 1 + 2 =>$  контролируется битами К1 и К2

**И2:** поз.  $5 => 5 = 2^0 + 2^2 = 1 + 4 =>$  контролируется битами К1 и К3

**Из:** поз.  $6 => 6 = 2^1 + 2^4 = 2 + 4 =>$  контролируется битами К2 и К3

**И4:** поз. 7 => 7 =  $2^0 + 2^1 + 2^2 = 1 + 2 + 4 =>$  контролируется битами К1, К2 и К3

**И**<sub>5</sub>: поз.  $9 \Rightarrow 9 = 2^0 + 2^3 = 1 + 8 \Rightarrow$  контролируется битами К1 и К4

**И6:** поз.  $10 \Rightarrow 7 = 2^1 + 2^3 = 2 + 8 \Rightarrow$  контролируется битами К2 и К4

**И**<sub>7</sub>: поз.  $11 = 7 = 2^0 + 2^1 + 2^3 = 1 + 2 + 8 = >$  контролируется битами К1, К2 и К4

**И**8: поз.  $12 => 12 = 2^2 + 2^3 = 4 + 8 =>$  контролируется битами К3 и К4

По полученным расчетам можно определить группы информационных бит для каждого контрольного бита:

$$K_1 = H_1 + H_2 + H_4 + H_5 + H_7$$

$$K_2 = H_1 + H_3 + H_4 + H_6 + H_7 + H_8$$

$$K_3 = H_2 + H_3 + H_4 + H_8$$

$$K_4 = H_5 + H_6 + H_7 + H_8$$

Таким образом, зная значения контрольных бит, можно получить кодовое слово (КС), передаваемое по каналу связи. Для исправления однократной ошибки необходимо на приёмной стороне осуществить контроль четности каждой информационной группы:

**K**<sub>1</sub>:

$$K_1 + U_1 + U_2 + U_4 + U_5 + U_7$$

**K**<sub>2</sub>:  $K_2 + U_1 + U_3 + U_4 + U_6 + U_7$

**K**<sub>3</sub>:  $K_3 + U_2 + U_3 + U_4 + U_8$

**K**<sub>4</sub>:  $K_4 + U_5 + U_6 + U_7 + U_8$

В тех группах, где сумма информационных и контрольных бит не равна нулю, содержится ошибка. Если ошибка только одна, то она должна быть в одном из битов, принадлежащих обеим группам. Для того, чтобы уточнить, в каком именно бите произошла ошибка, нужно обратиться к группам, в которых проверка на четность прошла успешно, а, следовательно, в этих группах все биты корректны. Таким образом, исправление однократной ошибки осуществляется систематически с применением линейных комбинаций информационных и контрольных бит.

Преимуществами кодов Хэмминга являются простота аппаратной реализации, небольшая избыточность (для кодирования 7 бит данных избыточность составляет чуть больше 57%, для кодирования 256 бит избыточность равна 3,5%, а для 1024 — 1%). Существенным недостатком является ограниченное количество исправляемых ошибок. Это ограничивает область применения данного типа кодов.

Существуют также циклические коды Хэмминга, в которых контрольные разряды размещаются в конце кодового слова. Построение таких кодов основано на операциях с образующими многочленами (полиномами), а их декодирование осуществляется способами, применяемыми для циклических кодов.

#### Код Голея

Данный вид кодов, позволяющий обнаруживать и исправлять ошибки кратности до трех включительно, был открыт швейцарским математиком Голеем. Применялся в программном обеспечении космических аппаратов Вояджер для передачи изображений. В настоящее время применяется в радиостанциях, работающих на низких радиочастотах и передающих информацию друг другу за несколько тысяч километров.

В основе идеи кода Голея лежит формула [43, 49] для определения количества проверочных разрядов k, которая имеет следующий вид:

$C^0_n + C^1_n + \ldots + C^i_n = 2^k$ , где  $t_i$  – количество исправляемых ошибок, а  $C^i_n$  – число сочетаний из n по i. Занимаясь поиском совершенных кодов, Голей заметил, что  $C^0_{23} + C^1_{23} + C^3_{23} = 2^{11}$ . Это говорит о возможности существования совершенного двоичного кода (23,12), где n = 23, m = 12, k = 11, исправляющего все ошибки кратности до трёх включительно. В данном случае под совершенным кодом подразумевается такой код, в котором число избыточных (контрольных) разрядов ровно столько, сколько нужно для исправления заданного количества ошибок. На данный момент известно только 2 вида совершенных кодов — это код Хэмминга (для однократных ошибок) и код Голея (для трёхкратных ошибок) [43].

Для декодирования кодов Голея применяется циклический алгоритм декодирования, описанный в разделе 3.4.2. Недостатком кода является его ограниченная длина: код можно построить только для длины информационного блока, равной 12. Это сужает область применения данного типа кодов.

### 1.3.2. Полиномиальные циклические коды

Полиномиальные коды подразумевают представление кодового слова  $C = (c_0, c_1, ..., c_{n-1})$  в виде многочлена  $C(x) = c_0 + c_{1*}x + ... + c_{n-1*}x^{n-1}$ . Применяя данное обозначение, можно определить полиномиальный код как множество всех многочленов степени, не большей n-1, содержащих в качестве множителя некоторый фиксированный многочлен G(x), называемым *образующим многочленом* (полиномом) [43].

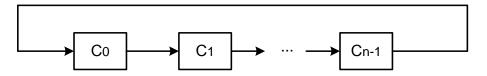

В полиномиальных циклических кодах любой циклический сдвиг любого кодового слова является другим кодовым словом [43]. В полиномиальном представлении циклический сдвиг на одну позицию  $C^{l}(x)$  соответствует умножению на x по модулю  $(x^{n}-1)$ :

$$C^{I}(x) = xC(x)mod(x^{n} - 1).$$

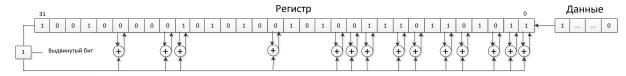

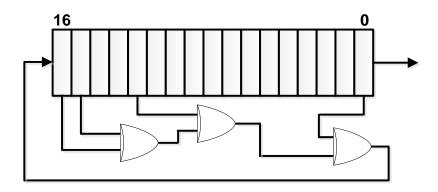

Операция циклического сдвига реализуется на регистрах сдвига (рисунок 1.3).

Рисунок 1.3 – Сдвиг кодового слова вправо

В теории циклических кодов для получения образующих многочленов используют многочлены, делящиеся без остатка на себя и на единицу, которые также называют *неприводимым минимальным многочленом (полиномом)*. Образующий многочлен может быть равен неприводимому минимальному многочлену  $\Phi(x)$  или являться произведением нескольких неприводимых многочленов:

$$G(x) = \Phi_1(x)\Phi_2(x)\dots\Phi_i(x).$$

#### Построение полиномиальных циклических кодов

Одним из способов построения циклического кода (кодирования) является применение образующей матрицы G(x) [50]. Несмотря на то, что на практике применяются в основном циклические коды, принадлежащие к классу систематических кодов, существуют также несистематические циклические

коды. Для несистематических циклических кодов образующая матрица получается в результате m-кратного циклического сдвига первой строки образующей матрицы, которая в свою очередь получается дополнением G(x) слева нулями до длины кодовой комбинации, равной n [50]. В полиномиальном виде образующая матрица для несистематического циклического кода будет иметь вид:

$$G = \begin{cases} G(x) \\ xG(x) \\ x^2G(x) \\ \dots \\ x^{m-1}G(x) \end{cases}$$

Для того чтобы получить кодовое слово необходимо информационное сообщение M = (M0, M1, M2, ...., Mm-1) умножить по модулю 2 на матрицу G:

$$C(x) = M(x) \cdot G = Mo \cdot G(x) xor M1 \cdot xG(x) xor M2 \cdot x^2G(x) xor ... xor Mm-1 \cdot x^{m-1}G(x)$$

Для построения несистематического циклического кода без образующей матрицы необходимо полином, представляющий информационный блок, умножить по модулю 2 на образующий полином [50]:

$$C(x) = M(x) \cdot G(x)$$

.

Для построения образующей матрицы систематического циклического кода необходимо составить диагональную транспонированную матрицу  $E^T$ , в которой число строк и столбов равно длине информационного блока, а также дополнительную матрицу G, в которой размещаются остатки от деления полиномов  $x^{n-k} \dots x^{n-1}$  на образующий полином по следующему принципу:

$$G' = \begin{bmatrix} x^{n-1} modG(x) \\ x^{n-k+1} modG(x) \\ \dots \\ x^{n-k} modG(x) \end{bmatrix}$$

Например, для кода (15,7), где n=15, m=7,  $G(x)=x^8+x^7+x^6+x^4+1$  диагональная матрица будет иметь вид:

$$E^{T} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 0 & 0 & 0 \end{bmatrix}$$

Дополнительная матрица будет иметь вид:

$$G' = \begin{bmatrix} 1 & 1 & 1 & 0 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 1 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 1 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 0 & 1 \\ 1 & 1 & 1 & 0 & 0 & 1 & 1 & 0 \\ 0 & 1 & 1 & 1 & 0 & 0 & 0 & 1 \end{bmatrix}$$

Образующая матрица получается путём совмещения диагональной и дополнительной матриц:

Систематическое кодирование с помощью образующей матрицы осуществляется следующим образом:

$$C(x) = M(x) \cdot x^{n-k} xor M(x) \cdot x^{n-k} \cdot G.$$

(1.2)

Из выражения 1.2 видно, что в систематическом коде информационные (выражение  $M(x) \cdot x^{n-k}$ ) и контрольные разряды (выражение  $M(x) \cdot x^{n-k} \cdot G$ ) кодового слова разделены, при этом контрольные символы являются линейной комбинацией информационных символов.

Без применения образующей матрицы систематический циклический код строится следующим образом:

$$C(x) = M(x) \cdot x^{n-k} xor M(x) \cdot x^{n-k} mod G(x).$$

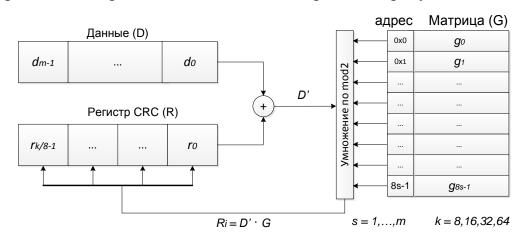

Таким образом, в циклических кодах вычисление остатка от деления эквивалентно умножению по модулю 2 на предварительно вычисленную образующую матрицу.

### Декодирование полиномиальных циклических кодов

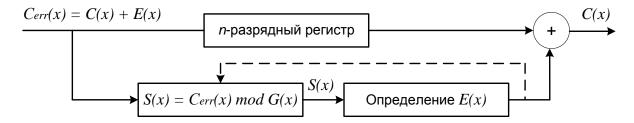

Задача декодирования полиномиальных циклических кодов сводится к поиску полинома ошибок E(x) в уравнении Cerr(x) = C(x) + E(x).

Для определения полинома ошибок E(x) используется синдром ошибки S(x), который определяется выражением:

$$S(x) = E(x) \bmod G(x) = Cerr(x) \bmod G(x). \tag{1.3}$$

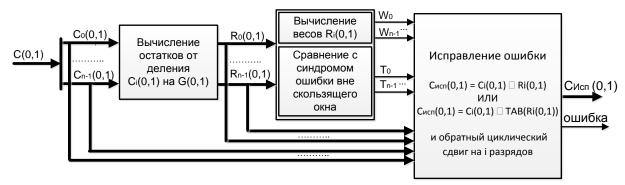

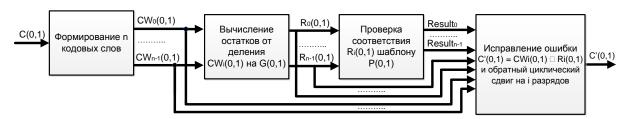

На рисунке 1.4 приведена обобщенная схема декодирования циклических кодов.

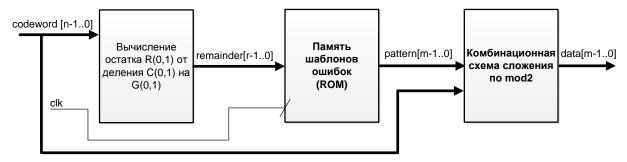

Рисунок 1.4 – Структурная схема поиска полинома ошибок

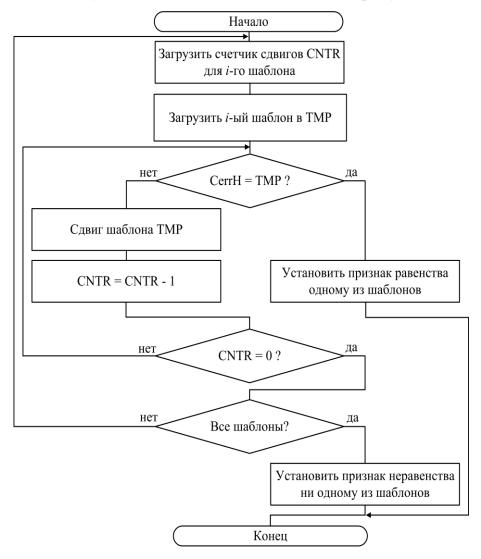

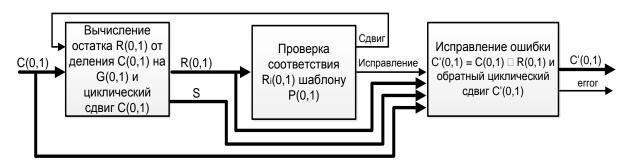

Уравнение (1.3) является основой для построения табличного (синдромного) декодера циклического кода, в котором синдром S(0,1) является адресом соответствующего шаблона ошибки E(0,1) [50]. При аппаратной реализации такого декодера требуется  $n \cdot 2^k$  (где n — длина кодового слова, k — длина контрольного блока) бит памяти для хранения таблицы шаблонов ошибок.

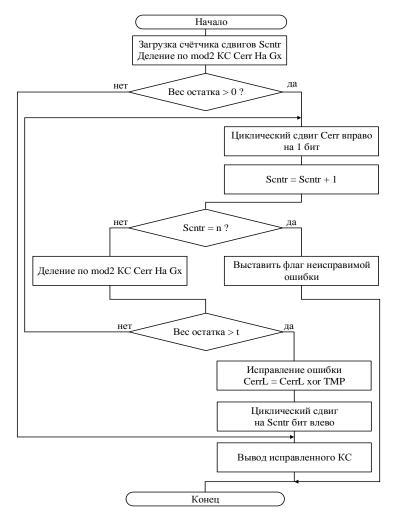

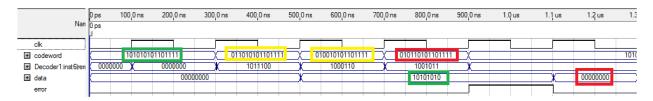

Другой вариант декодера основан на циклическом алгоритме декодирования [50], который заключается в последовательном выполнении нескольких этапов:

- 1) Кодовое слово с ошибкой  $C_{err}(0,1)$  делится на образующий полином G(0,1);

- 2) Вычисляется вес (количество единиц кода) w синдрома S(0,1). Если  $w \le t$  (t количество исправляемых ошибок), то  $C(0,1) = C_{err}(0,1)$  xor S(0,1) и исправленное кодовое слово подаётся на выход декодера. Eсли w > t, то осуществляется переход на этап 3.

- 3) Кодовое слово C(0,1) циклически сдвигается на 1 разряд влево (или вправо). Полученное кодовое слово C'(0,1) делится на образующий полином G(0,1). Если  $w \le t$ , то C(0,1) = C'(0,1) xor S(0,1), результат циклически сдвигается обратно (относительно направления сдвига до G(0,1)количеству деления на на количество разрядов, равное предшествующих сдвигов. Исправленное кодовое слово подаётся на выход декодера.  $E c \pi u + v > t$ , то этап 3 повторяется. Если количество сдвигов достигает n-1 и ошибка не обнаружена (условие  $w \le t$  не выполнилось ни на одной из итераций), то ошибка считается неисправимой для данного декодера.

Для реализации циклического алгоритма декодирования не требуется память для хранения шаблонов ошибок. Однако данный алгоритм значительно уступает в быстродействии табличному алгоритму в виду многократного применения операций циклического сдвига и деления полиномов. Также

недостатком описанного циклического алгоритма является невозможность исправлять ошибки для кодов, в которых m > k, т.е. когда длина информационного блока больше длины контрольного блока. Данный недостаток связан с понятием *скользящее окно* — область кода, в которой ошибки заданной кратности будут гарантировано исправляться циклическим алгоритмом декодирования. Длина скользящего окна равна длине контрольного блока кода, поэтому в случаях, когда длина сообщения m > k циклический алгоритм декодирования будет работать не для всех возможных ошибок кратности t. Это обусловлено тем, что некоторые ошибки кратности t выйдут за диапазон скользящего окна. Табличный алгоритм декодирования данным недостатком не обладает.

Таким образом, для декодирования циклических кодов является актуальным разработка быстродействующего и эффективного алгоритма декодирования, совмещающего достоинства табличного и циклического способов декодирования.

# Циклические коды Боуза-Чоудхури-Хоквингема

Коды Боуза-Чоудхури-Хоквингема (БЧХ) представляют собой обширный класс кодов с минимальным кодовым расстоянием  $d_{\min} \ge 2 \cdot t + 1$ , исправляющих несколько ошибок. Конструкция кодов БЧХ определяется корнями образующего многочлена [43]. Образующий многочлен циклического кода БЧХ является наименьшим общим кратным (НОК) нечетных минимальных многочленов:

$$G(x) = \text{HOK}[\Phi_1(x), \Phi_3(x), ..., \Phi_{2t-1}(x)]$$

где t – количество исправляемых ошибок,  $\Phi i(x)$  – минимальный неприводимый многочлен.

Число минимальных многочленов, необходимых для построения кода БЧХ, равно t. Максимальный порядок минимальных многочленов вычисляется по формуле:  $p = 2 \cdot t - 1$ .

Длина кода БЧХ должна соответствовать выражению  $n = 2^h - 1$ , где h - 1 любое целое число [50]. В таблице 1.3. приведены минимальные неприводимые многочлены для  $h \in [2;7]$  степени многочлена l = 1,3,5,...15.

| 1       | Мин | нимальны | е непривод | цимые мно | гочлены пр | и значении | степени h  |

|---------|-----|----------|------------|-----------|------------|------------|------------|

| $\iota$ | 2   | 3        | 4          | 5         | 6          | 7          | 8          |

| 1       | 111 | 1011     | 10011      | 100101    | 1000011    | 10001001   | 100011101  |

| 3       | _   | 1101     | 11111      | 111101    | 1010111    | 10001111   | 101110111  |

| 5       | _   | 111      | 110111     | 1100111   | 10011101   | 111110011  | 1100110001 |

| 7       | _   | _        | 11001      | 101111    | 1001001    | 11110111   | 101101001  |

| 9       | _   | _        | _          | 1101111   | 1101       | 10111111   | 110111101  |

| 11      | _   | _        | _          | 111011    | 1101101    | 11010101   | 111100111  |

| 13      | _   | _        | _          | _         | _          | 10000011   | 100101011  |

| 15      | _   | _        | _          | _         | _          | _          | 111010111  |

| 17      | _   | _        | _          | _         | _          | _          | 010011     |

| 19      | _   | _        | _          | _         | _          | 10000011   | 101100101  |

| 21      | _   | _        | _          | _         | _          | 11001011   | 110001011  |

Таблица 1.3 – Двоичное представление неприводимых многочленов

Например, для построения образующего полинома кода длиной n=15, исправляющего t=2 ошибки, необходимо выполнить следующие операции:

- 1) вычислить степень  $h = \log_2(n+1) = 4$ ;

- 2) из таблицы 1.3 выбрать t=2 минимальных неприводимых многочленов, степень старшего из которых равна  $p=2 \cdot t-1=3$ ;

- 3) Вычислить произведение  $G(0,1) = \Phi_I(0,1) \cdot \Phi_2(0,1) = 10011 \cdot 111111 = 111010001 => <math>G(x) = x^8 + x^7 + x^6 + x^4 + 1$ .

Построение циклического кода БЧХ осуществляется одним из систематических способов, описанных ранее.

Особенностью и недостатком кодов БЧХ является то, что для исправления числа ошибок  $t \geq 2$  еще недостаточно условия, чтобы между комбинациями кода минимальное кодовое расстояние было равно  $d_{\min}=2 \cdot t+1$ . Необходимо также, чтобы длина кода n удовлетворяла условию  $n=2^h-1$ , где h-любое целое число [43].

В таблице 1.4. приведены примеры БЧХ кодов (m-длина информационного блока, k — длина контрольного блока) для различных длин кодовых слов n и кратности исправляемых ошибок t [41].

Таблица 1.4 – Параметры кодов БЧХ (n, m, k)

| n  | m  | k  | t  | d  | m/n  |

|----|----|----|----|----|------|

| 7  | 4  | 3  | 1  | 3  | 0,57 |

| 15 | 11 | 4  | 1  | 3  | 0,73 |

| 15 | 7  | 8  | 2  | 5  | 0,47 |

| 15 | 5  | 10 | 3  | 7  | 0,33 |

| 31 | 26 | 5  | 1  | 3  | 0,84 |

| 31 | 21 | 10 | 2  | 5  | 0,68 |

| 31 | 16 | 15 | 3  | 7  | 0,52 |

| 31 | 11 | 20 | 5  | 11 | 0,35 |

| 31 | 6  | 25 | 7  | 15 | 0,19 |

| 63 | 57 | 6  | 1  | 3  | 0,9  |

| 63 | 51 | 12 | 2  | 5  | 0,81 |

| 63 | 45 | 18 | 3  | 7  | 0,72 |

| 63 | 39 | 24 | 4  | 9  | 0,62 |

| 63 | 36 | 27 | 5  | 11 | 0,57 |

| 63 | 30 | 33 | 6  | 13 | 0,48 |

| 63 | 24 | 39 | 7  | 15 | 0,37 |

| 63 | 18 | 45 | 10 | 21 | 0,29 |

| 63 | 16 | 47 | 11 | 23 | 0,25 |

| 63 | 10 | 53 | 13 | 27 | 0,16 |

| 63 | 7  | 56 | 15 | 31 | 0,11 |

Первая строка таблицы 1.4 соответствует коду Хэмминга. При увеличении кратности ошибок t повышается избыточность кода, что видно из соотношения m/n, которое называется cкоростью кода. Значение длины кода n всегда будет нечетным числом:  $n=1,3,5,...(2^h-1)$ , т.е. не все длины информационных сообщений m могут быть заданы, при этом значение n определяет число контрольных символов k:  $k <= h \cdot t <= [\log_2(n+1)] \cdot t$ . Данный недостаток может быть существенным при разработке кодеков помехоустойчивых кодов, в которых исходными параметрами являются длина информационного (неизбыточного) сообщения m и количество исправляемых

ошибок t. Одним из способов решения проблемы является укорачивание БЧХ кода путём уменьшения разрядности информационного блока с сохранением разрядности контрольного блока. Однако это приводит к повышению избыточности, потере цикличности и эффективности кода. Заметим, что длина и избыточность кода зависит от длины образующего полинома, поэтому одним из способов увеличения длин информационного блока m может быть применение такого алгоритма построения образующего полинома, который позволит получить эффективные образующие полиномы для любых значений m. Такие полиномы следует искать с помощью программных и вычислительных средств, исходя их двух параметров: m — длина информационного блока и t — кратность исправляемых ошибок.

# Декодирование циклических кодов БЧХ

При реализации декодеров БЧХ кодов обычно используют способ, основанный на применении элементов поля Галуа или конечного поля для нумерации позиций кодового слова [43, 49, 51].

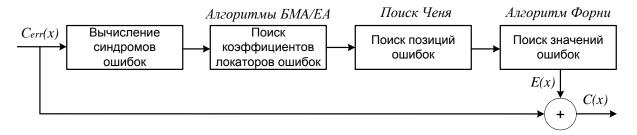

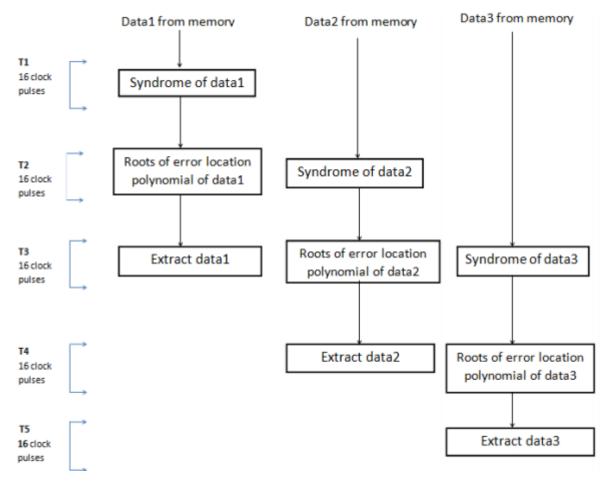

Процесс декодирования (рисунок 1.5) заключается в последовательном выполнении этапов:

- 1) Вычисление синдромов ошибок;

- 2) Поиск коэффициентов локаторов ошибок;

- 3) Поиск позиций ошибок в кодовом слове;

- 4) Поиск значений ошибок (для недвоичных кодов);

- 5) Исправление ошибок на вычисленных позициях.

Рисунок 1.5 – Общая схема декодирования БЧХ кодов

Позиции ошибок находятся из решения системы уравнений в поле Галуа  $GF(2^k)$ , где k — старшая степень образующего многочлена (таблица 1.5). Систему уравнений можно получить, введя многочлен ошибок E(x) и учитывая нули кода  $\alpha^j$  для  $b \le j \le b + 2t_d - 1$ , где  $t_d$  — количество ошибок в принятом кодовом слове, при этом количество исправляемых ошибок декодером  $t \le t_d$ .

Позиции ошибок находятся из решения системы уравнений в поле Галуа  $GF(2^k)$ , где k — старшая степень образующего многочлена. Систему уравнений можно получить, введя многочлен ошибок E(x) и учитывая нули кода  $\alpha^j$  для  $b \le j \le b + 2t_d - 1$ , где  $t_d$  — количество ошибок в принятом кодовом слове, при этом количество исправляемых ошибок декодером  $t \le t_d$ .

Если кодовое слово с ошибкой задается уравнением  $C_{err}(x) = C(x) + E(x)$ , то многочлен ошибок определяется как:

$$E(x) = e_{ji}x^{ji} + e_{j2}x^{j2} + ... + e_{jt}.$$

(1.4)

Множества {  $e_{jl}, e_{j2}, ...., e_{jt}$  }, где  $e_{jl} \in \{0,1\}$  (для двоичных кодов), и {  $\alpha^{j_1}$ ,  $\alpha^{j_2}, ..., \alpha^{jt}$ }, где  $\alpha^j \in GF(2^k)$  являются локаторами ошибок.

Таблица 1.5 – Нумераций позиций КС в полях Галуа

| Символы КС          | $C_0$ | $C_{I}$ | $C_2$      | ••• | $C_{n-1}$      |

|---------------------|-------|---------|------------|-----|----------------|

| Локаторы<br>позиций | 1     | α       | $\alpha^2$ |     | $\alpha^{n-1}$ |

Исходя из выражения (1.4) и определения полей Галуа, вычисляются синдромы ошибок как значения принятого кодового слова в нулях кода и тем самым выполняется первый этап декодирования (рисунок 1.5):

$$S_{I} = C_{err}(\alpha^{b}) = e_{j1} \alpha^{bj_{1}} + ... + e_{jt} \alpha^{bjt},$$

$S_{2} = C_{err}(\alpha^{b+1}) = e_{j1} \alpha^{(b+1)j_{1}} + ... + e_{jt} \alpha^{(b+1)jt},$

$\cdot S_{2td} = C_{err}(\alpha^{b+2td-1}) = e_{j1} \alpha^{(b+2td-1)j_{1}} + ... + e_{jt} \alpha^{(b+2td-1)jt}.$

Поиск коэффициентов локаторов ошибок (этап 2 процесса декодирования) заключается в решении ключевого уравнения:

$$\begin{pmatrix}

S_1 \\

S_2 \\

\vdots \\

S_{2t}

\end{pmatrix} = \begin{pmatrix}

S_1 & S_2 & \cdots & S_t \\

S_2 & S_3 & \cdots & S_{t+1} \\

\vdots & \vdots & \ddots & \vdots \\

S_t & S_{t+1} & \cdots & S_{2t-1}

\end{pmatrix} \begin{pmatrix}

\sigma_t \\

\sigma_{t-1} \\

\vdots \\

\sigma_1

\end{pmatrix}.$$

(1.5)

При этом многочлен локаторов ошибок имеет вид:

$$\sigma_t(x) = \prod_{l=1}^t (1 + \alpha^{j_l} x) = 1 + \sigma_1 x + \sigma_2 x^2 + \dots + \sigma_t.$$

Решение уравнения (1.5) является трудоёмкой задачей и требует интенсивных вычислений. Известны различные алгоритмы решения ключевого уравнения, ориентированные как на программные (алгоритм Берлекемпа-Месси, алгоритм Питерсона-Горленштейна-Цирлера), так и на аппаратные реализации (Евклидов алгоритм) [43, 53–56].

# Алгоритм Берлекемпа-Месси

Алгоритм Берлекемпа-Месси [52, 53] представляет собой итеративный процесс построения многочлена обратной связи  $\sigma^{(i+1)}(x)$  наименьшей степени, удовлетворяющего следующему уравнению, полученному из (1.5):

$$\sum_{j=0}^{l_i+1} S_{k-j} \sigma_j^{(i+1)} = 0$$

, где  $l_i < k < i+1$ . (1.6)

Решение этой задачи эквивалентно условию, что многочлен

$$\sigma^{(i+1)}(x) = 1 + \sigma_1^{(i+1)}x + \dots + \sigma_{l_{i+1}}^{(i+1)}x^{l_{i+1}}$$

является многочленом обратной связи линейного регистра сдвига с обратной связью (ЛРОС), который генерирует ограниченную последовательность синдромов.

При решении данной задачи вводится понятие несовместность — расхождение на i-ой итерации, которое определяется как:

$$d_i = S_{i+1} + S_i \sigma_1^{(i)} + \dots + S_{i-l_i+1} \sigma_{l_i}^{(i)}.$$

(1.7)

Выражение (1.7) является мерой соответствия синдромной последовательности и генерируемой ЛРОС, а также содержит корректирующий множитель для вычислений на последующих итерациях.

Если  $d_i = 0$ , то уравнение (1.6) будет выполняться при:

$$\sigma^{i+1}(x) = \sigma^{i}(x), l_{i+1} = l_{i}.$$

Если  $d_i \neq 0$ , то решение на следующей итерации примет вид:

$$\sigma^{i+1}(x) = \sigma^{i}(x) + d_{i}d_{m}^{-1}x^{i-m},$$

$$l_{i+1} = \max\{l_{i}, l_{m} + i - m\}.$$

При этом должно выполняться условие:  $-1 \le m \le i$ .

Итеративное выполнение алгоритма продолжается до тех пор, пока выполняются одно или оба из условий проверки:

- 1) либо  $i \ge l_{i+1} + t_d 1$ ;

- 2) либо  $i = 2t_d 1$

При этом начальными условиями алгоритма являются:

$$\sigma^{(-1)}(x) = 1$$

,  $l_{-1} = 0$ ,  $d_{-1} = 1$ ,  $\sigma^{(0)}(x) = 1$ ,  $l_0 = 0$ ,  $d_0 = S_1$ .

По числу операций в конечном поле  $GF(2^k)$  БМА считается эффективным, однако алгоритм не является хорошо адаптированным для аппаратных реализаций ввиду наличия последовательных (зависимых) итераций и условных переходов. Вследствие этого используется в основном в программных реализациях [54] для моделирования работы кодеков БЧХ кода. Для аппаратного решения (на ПЛИС) ключевого уравнения наиболее приемлемым является Евклидов алгоритм [43], идея которого заключается в поиске наибольшего общего делителя (НОД) двух полиномов.

# Алгоритм Евклида

В алгоритме Евклида [43] для нахождения локатора ошибок определяется полином значений ошибок через синдромный полином в виде  $E(x) = \sigma(x)S(x)$ , где  $S(x) = 1 + S_1x + \dots + S_{2td}x^{2td}$ .

Из системы уравнений (1.5) следует, что  $E(x) = \sigma(x)S(x) \operatorname{mod}(x^{2td+1})$ . Для поиска многочлена E(x) применяется расширенный алгоритм Евклида к многочленам  $r_0(x) = x^d$ , где  $d = 2t_d + 1$  и  $r_1(x) = S(x)$ . Если на j-ом шаге алгоритма получено решение  $r_j(x) = a_j(x)x^{2td+1} + b_j(x)S(x)$ , причем  $\deg[r_j(x)] \leq t_d$ , то  $E(x) = r_j(x)$  и  $\sigma_0(x) = b_j(x)$ .

Непосредственно процесс декодирования является итеративным и заключается в решении задачи вычисления НОД  $(r_0(x), r_1(x))$ :

- 1) Входные значения:  $r_0(x)$ ,  $r_1(x)$ ,  $\deg[r_0(x)] \ge \deg[r_1(x)]$ ;

- 2) Начальные условия:  $a_0(x) = 1$ ,  $b_0(x) = 0$ ,  $a_1(x) = 0$ ,  $b_1(x) = 1$ ;

- 3) На ј-ом шаге, при условии, что ј $\geq$ 2, выполняется длинное деление для многочленов  $r_{i-2}(x)$  и  $r_{i-1}(x)$ .

В результате будет получено

$$r_{j-2}(x) = q_j(x)r_{j-1}(x) + r_j(x), \quad 0 \le \deg[r_j(x)] \le \deg[r_{j-1}(x)];$$

4) Вычисляется

$$a_j(x) = a_{j-2}(x) - q_j(x)a_{j-1}(x), \ b_j(x) = b_{j-2}(x) - q_j(x)b_{j-1}(x);$$

- 5) Останавливаются вычисления на итерации  $last=j_{last}$  в случае, если  $\deg[r_{last}(x)]=0;$

- 6) Выходные значения: НОД  $(r_0(x), r_1(x)) = r_k(x)$ , где k-такое наибольшее ненулевое целое, при котором будут выполняться неравенства:  $r_k(x) \neq 0$  и  $k \leq j_{last}$ .

Регулярность структуры алгоритма Евклида способствует широкому применению его в аппаратных реализациях декодеров кодов БЧХ и Рида-Соломона.

# Алгоритм Питерсона-Горленштейна-Цирлера

Существует также алгоритм Питерсона-Горленштейна-Цирлера [55], являющийся прямым решением системы уравнений (1.5), однако его сложность растёт как  $t^3$ , где t – корректирующая способность кода, поэтому он применим только для небольших значений t.

Основной проблемой прямого решения системы (1.5) является то, что неизвестно действительное число ошибок в кодовом слове. Необходимо проверять гипотезу о том, что число ошибок равно t.

Работа алгоритма начинается с предположения о том, что кодовое слово содержит максимальное количество ошибок  $t_{max} = t_d$ , а также вычисления определителя  $\Delta_i$  для  $i = t_{max} = t_d$ :

$$\Delta_{i} = det \begin{pmatrix} S_{1} & S_{2} & \cdots & S_{i} \\ S_{2} & S_{3} & \cdots & S_{i+1} \\ \vdots & \vdots & \ddots & \vdots \\ S_{i} & S_{i+1} & \cdots & S_{2i-1} \end{pmatrix}.$$

Если  $\Delta_i=0$ , то действительное число ошибок меньше, чем ta. Значение i уменьшается на единицу и снова проверяется условие  $\Delta_i=0$ . Процесс повторяется пока i>1.

Если  $\Delta_i \neq 0$ , то вычисляется обратная матрица синдромов для вычисления значения  $\sigma_1, \sigma_2, ..., \sigma_t$  из уравнения (1.5).

Если  $\Delta_i \neq 0$  и i=1, то регистрируется ошибка, неисправимая для декодера.

Все изложенные алгоритмы позволяют с разной степенью сложности реализовать второй и самый трудоёмкий этап декодирования БЧХ-кодов (рисунок 1.5), заключающий в поиске коэффициентов многочлена локаторов ошибок. Для поиска конкретных позиций ошибок в кодовом слове с помощью найденных локаторов применяется алгоритм поиска Ченя (3-й этап декодирования).

## Алгоритм поиска Ченя

Алгоритм Ченя [43] заключается в поиске корней многочлена локаторов ошибок  $\sigma(x)$  методом проб и ошибок, который подразумевает полный перебор всех ненулевых элементов поля  $\beta \in GF(2^k)$ , которые берутся по порядку  $I, \alpha$  и т.д. с проверкой условия  $\sigma(\beta^{-1}) = 0$ . Значения  $\beta$ , для которых  $\sigma(\beta^{-1}) = 0$ , будут указывать на номера позиций кодового слова, в которых содержатся ошибочные символы.

#### Коды Рида-Соломона

Пакетные ошибки, возникающие в процессе передачи (хранения) данных, являются частным случаем независимых ошибок. В помехоустойчивом

кодировании для исправления такого типа ошибок применяются недвоичные коды Рида-Соломона [4, 5, 43, 56], которые можно интерпретировать как частный случай недвоичных кодов БЧХ. Данные коды обладают меньшей избыточностью, но при этом их длины также ограничены согласно выражению  $2^{h}-1$ , где h — натуральное число. Важной особенностью является то, что единица измерения длины кодового слова – это один из элементов поля Галуа  $GF(2^k)$ , где k – старшая степень образующего многочлена. Таким образом, в качестве параметров (n,m) кодов Рида-Соломона указывается количество символов (n-длина кодового слова, m – длина информационного блока), разрядность каждого из которых равна k бит. В частности, нулями PC кода, tошибок, являются 2tпоследовательных исправляющего степеней примитивного элемента поля Галуа. Образующий многочлен для кода РС задаётся выражением

$$G(x) = \prod_{j=b}^{b+2td-1} (x - \alpha^i),$$

где b – целое число, обычно равное 0 или 1.

Принцип декодирования кодов PC аналогичен с декодированием двоичных кодов БЧХ (рисунок 1.5), за исключением нескольких отличий:

- образующий многочлен отличен от кодов БЧХ;

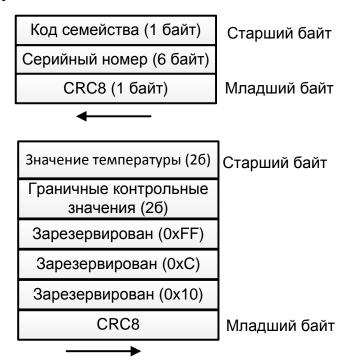

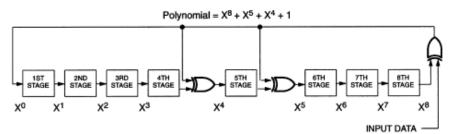

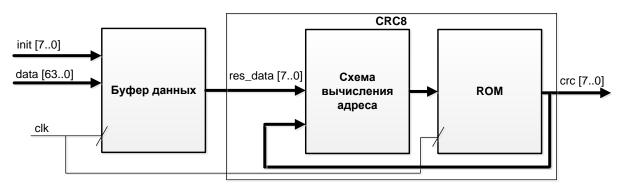

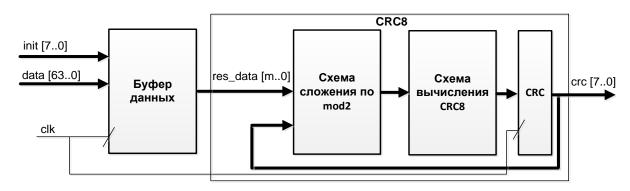

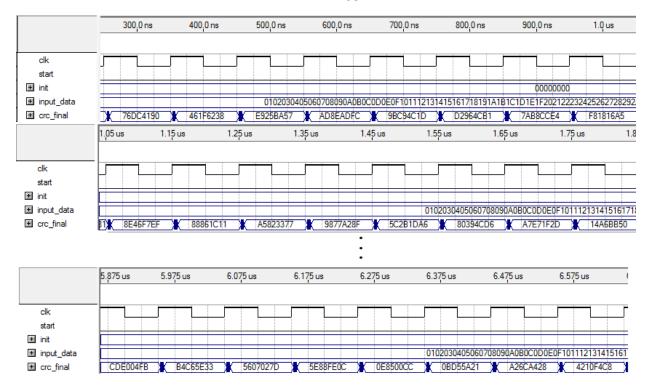

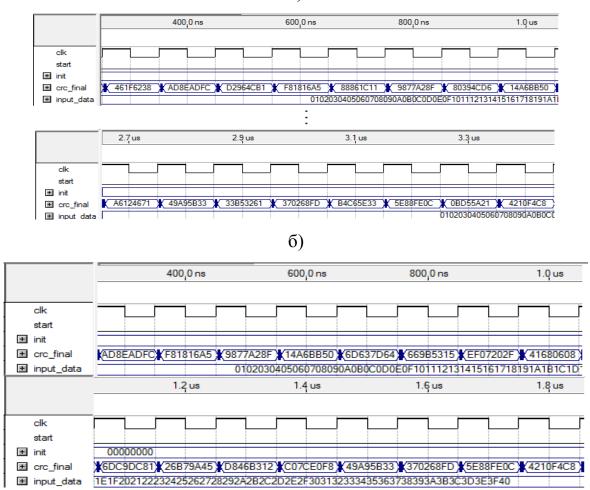

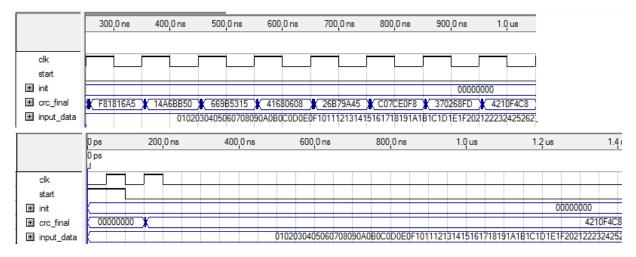

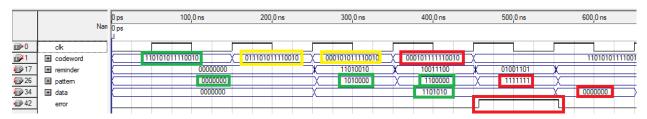

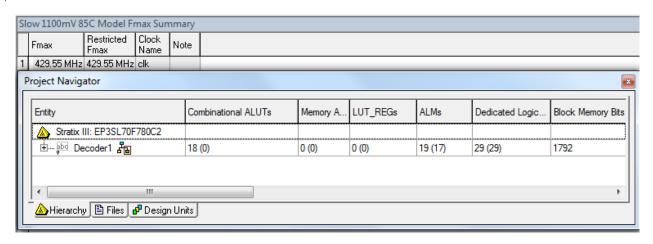

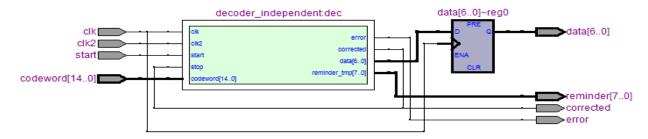

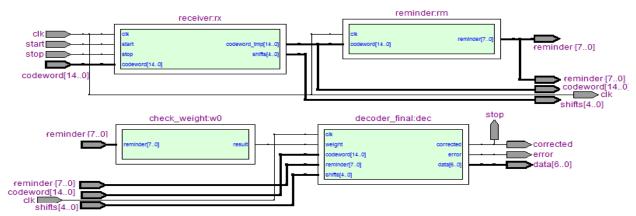

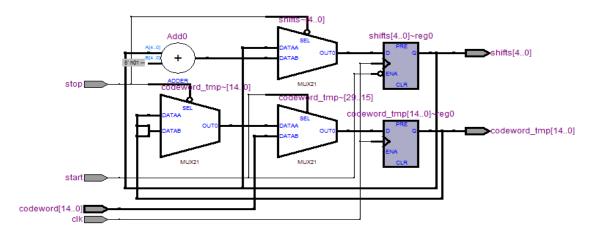

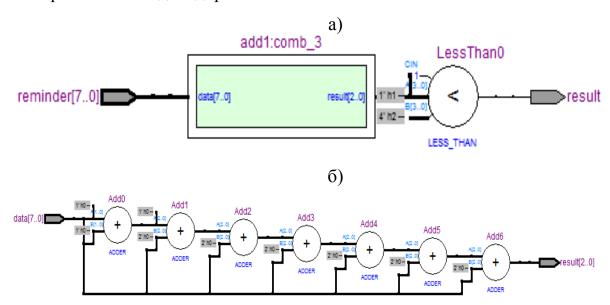

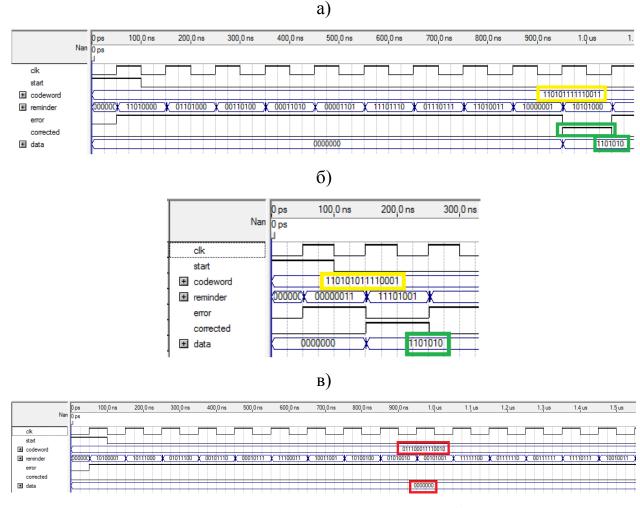

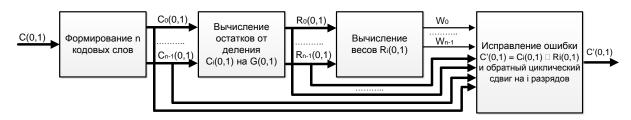

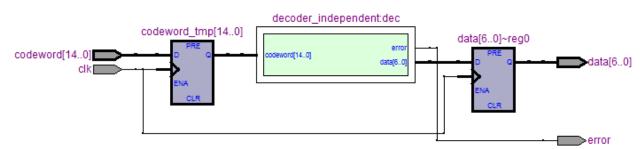

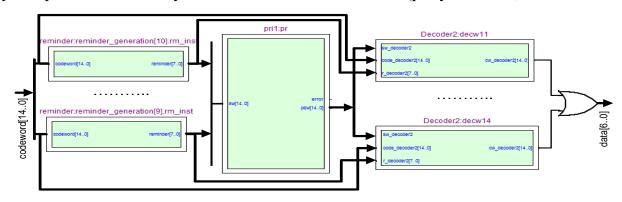

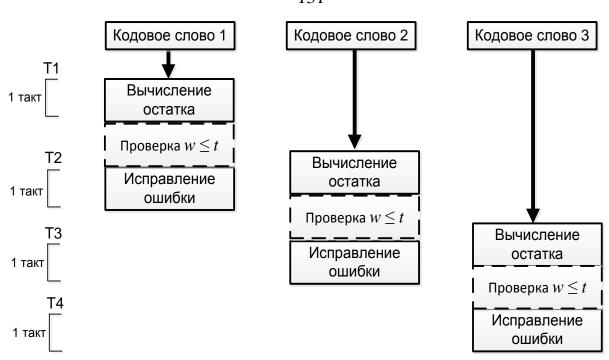

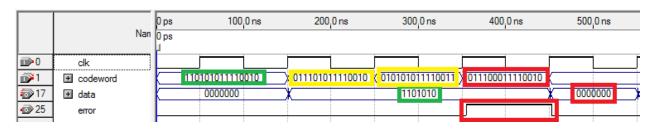

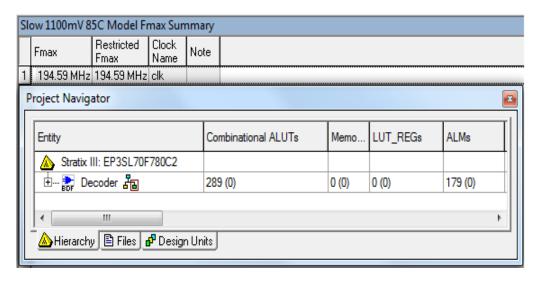

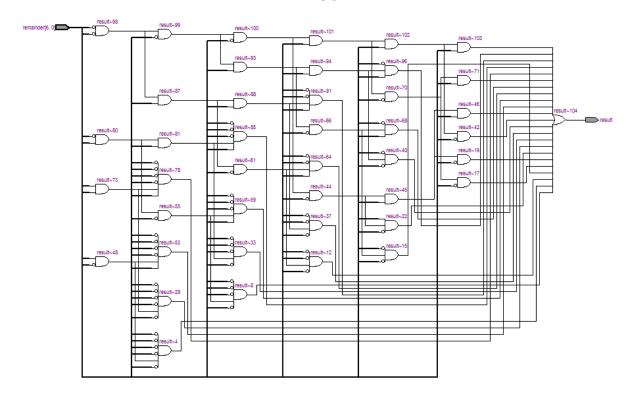

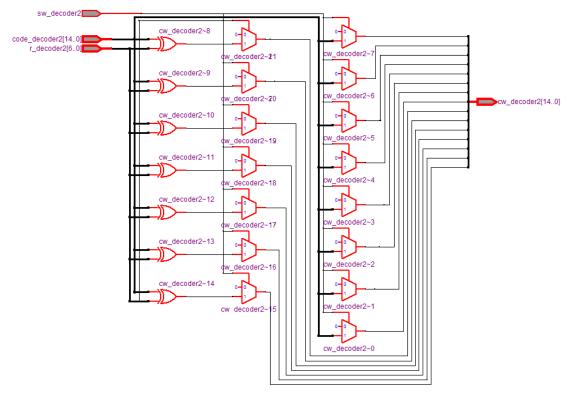

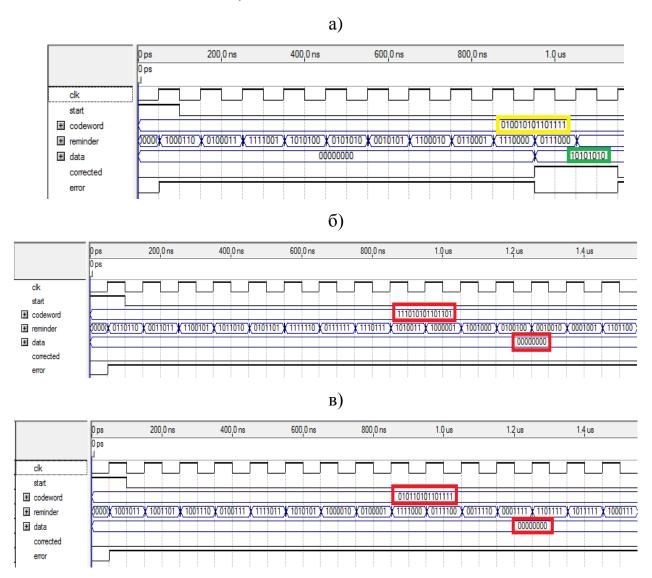

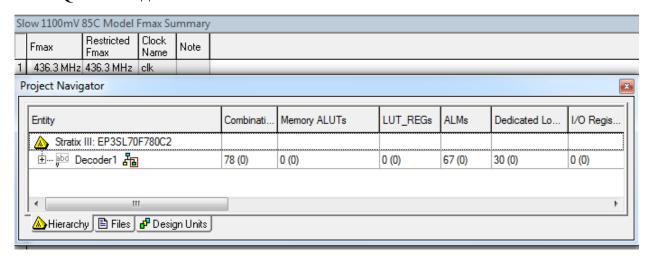

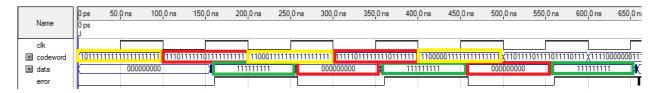

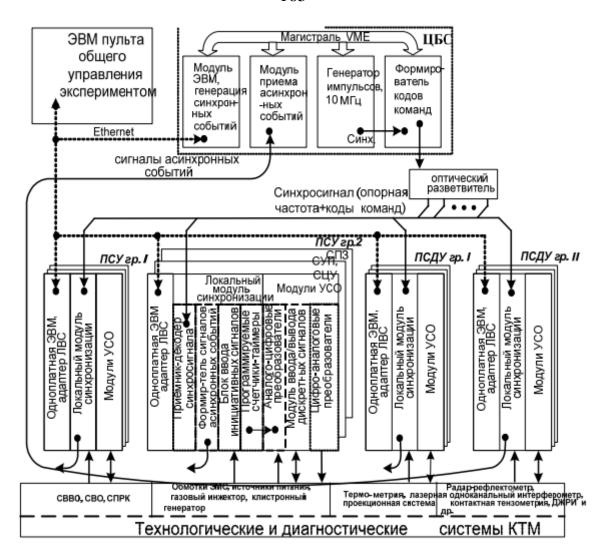

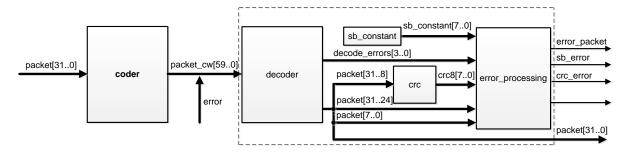

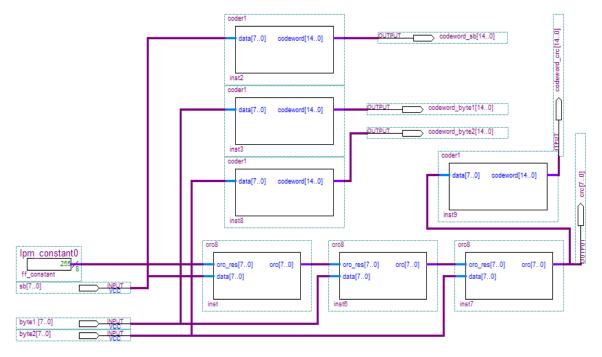

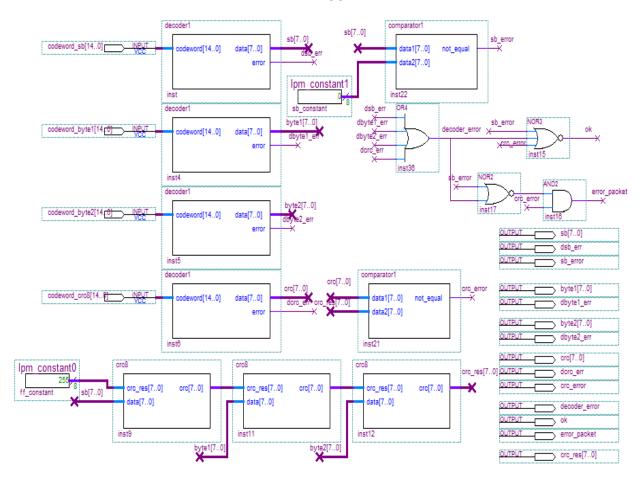

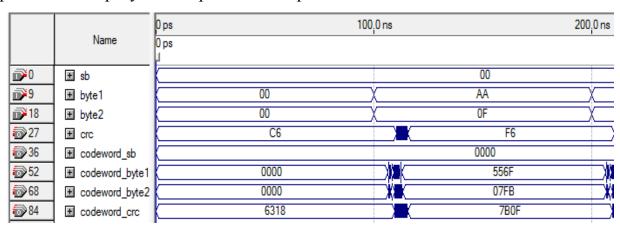

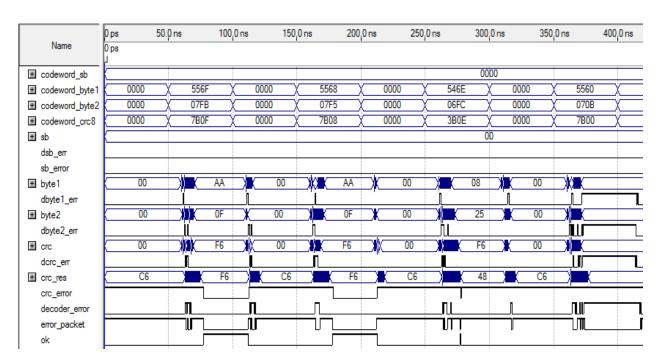

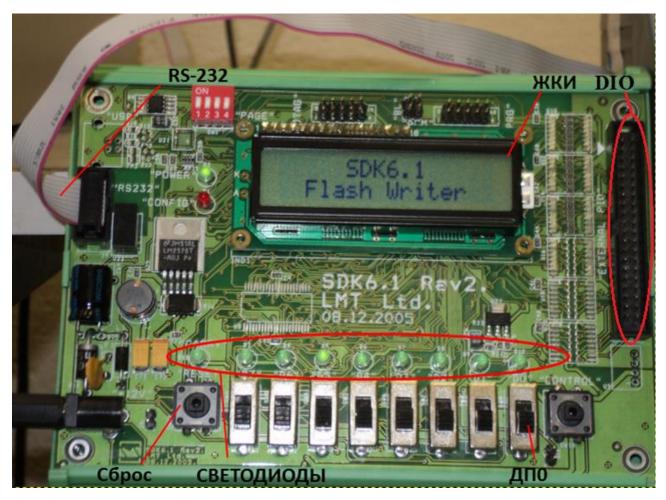

- коды ориентированы на исправление пакетов ошибок;